因為專業

所以領先

將存儲器疊層在邏輯器件上看似比較合理,這可以實現更大規模的小型化、性能和成本效益。然而,看似符合邏輯的想法卻并非如此簡單。因為邏輯處理器是邏輯加存儲配置或疊層中價值較高的器件,邏輯器件制造商在將他們的邏輯器件與存儲器件集成時遇到很大困難。他們預計購買晶圓形式的存儲器,但這并不是他們自身的產品,因此他們對存儲器件的測試良率、交互作用和質量非常關心。此外,存儲器測試的專業性非常強,最好留給存儲器制造商來完成,并可查看測試結果,以免遇到意想不到的復雜性和高成本。經過前期幾次倒霉的嘗試,大多數想將邏輯與存儲器件集成在同一封裝體內的邏輯器件制造商都在焦慮地尋找更好的方法。

PoP解決方案

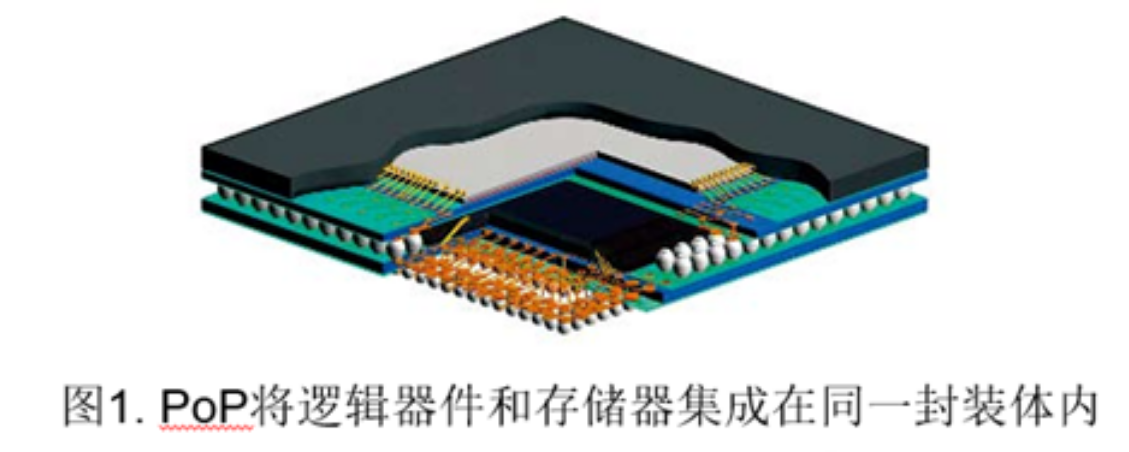

PoP被認為是更好的方案,可在同一封裝體內集成邏輯和存儲器件(圖1)。PoP的底部可

容納邏輯器件,這種封裝的底面可以處理高引腳數,要求器件采用微小的焊球間距。PoP的頂部可容納存儲器件或器件疊層。由于存儲器件一般要求引腳數較低,可以通過周邊陣列來處理,即在兩個封裝體互連的封裝邊緣處。封裝體的底部可以由邏輯器件制造商來制造和測試——每個都會影響他們核心的能力和技術。在一個封裝內集成外來的芯片所造成的責任問題可以消除了,因為每個制造商只負責他們自己的封裝。終端用戶、手持設備制造商可以通過調配來獲利,即傳統的存儲器供應商來供應頂部封裝,邏輯器件供應商來提供底部封裝。他們的配置也比較靈活,有多個存儲器貨源和封裝類型,可以與多個處理器封裝類型和供應商相匹配。

如果邏輯器件和存儲器件都被集成到同一個疊層封裝中,那么手機制造商則無需再列出特定的器件組合方案。通過JEDEC的電學(取決于內部存儲器的配置)和機械標準,可以靈活地實現頂部存儲器件封裝與底部邏輯器件封裝的組合。底部封裝也遵守JEDEC的機械標準。這樣的標準化允許制造商設計并生產能夠彼此兼容的產品,這也是為什么PoP終于成熟,并且在過去幾年內投放市場進行大量生產的一個基本原因。

今天,將PoP投入量產并不輕松,如同所有新型封裝技術一樣,還有很多障礙需要克服。為實現靈活的PoP結構,封裝疊層需要在PCB上同時塑模并再回流。此前并不容易實現,需要手機制造商或者其電子制造服務提供商(基板組裝)進行開發和優化。兩個球柵陣列(BGA)封裝不但可以在相互的頂部進行再回流,而且再回流兩個非常薄的、相對大些、窄間距的BGA在某種程度上也是新的挑戰。由于兩種封裝的間距都相對較窄(一般為0.65 mm的間距或者小于封裝體到封裝體之間的互連),再回流過程中每個封裝體能夠承受的翹曲量是非常有限的。以前,再回流過程中封裝翹曲并不是影響表面貼裝良率的主要考慮因素。

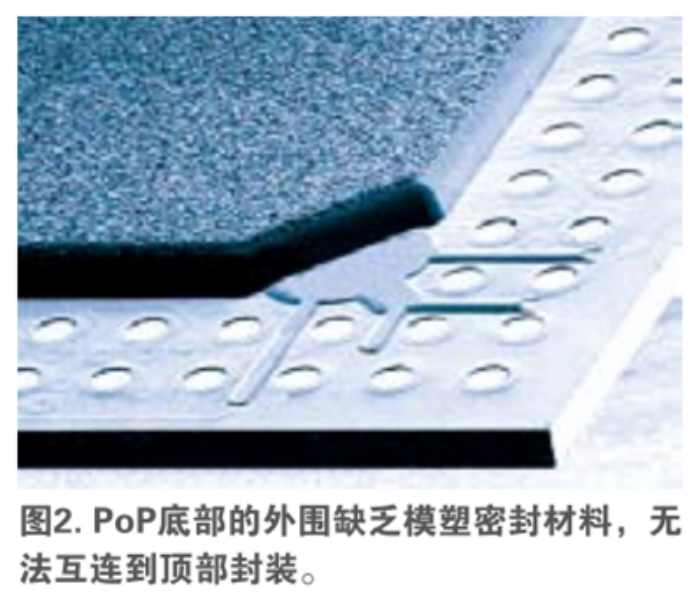

現在已經可以度量并控制封裝翹曲。使問題進一步復雜的原因是該結構很難控制底部PoP的翹曲。底部PoP的外圍缺乏模塑密封材料,可以互連到頂部封裝(圖2)。因此,外圍由一個無支持的封裝基板組成。為了降低整個疊層PoP的高度,基板又被盡可能地做薄。因為基板會由于再回流的溫度而膨脹(所有PoP都在稍高的再回流溫度下采用無鉛焊球,而非共晶錫鉛焊球),這樣的配置會內在的導致翹曲。封裝尺寸、器件尺寸、基板厚度和成分、模塑密封材料、裸片粘接厚度和材料全都在決定底部PoP翹曲中發揮重要作用。同樣地,必須對它們進行優化才可能生產出滿足表面組裝良率要求的底部PoP。一般而言,如果PoP疊層無法再回流到PCB上,就無法選擇重做,因此對于基板組裝時初次通過的良率要求是非常高的。

控制頂部封裝的翹曲也是一項挑戰。頂部PoP內部可疊層2至5片裸片。這些器件的尺寸各式各樣:一些器件尺寸相同或相近,需要在疊層裸片之間采用間隔夾層,這樣才能使引線鍵合到基板上。雖然再回流時觀察封裝的頂部會發現一般底部PoP的外形有些凹陷,然而頂部PoP的外形也會凹陷或凸起。盡管頂部PoP將模塑密封材料擴展到封裝邊緣,通常產生的翹曲小于底部PoP,頂部PoP的翹曲必須經常容忍底部封裝的翹曲或者保持繃緊狀態以允許底部封裝中更高的翹曲。封裝材料和厚度的優化對于頂部PoP實現合格的表面組裝良率是非常重要的。再回流過程中以頂部和底部封裝為目標的翹曲最初大約80μm。然而,隨著大量的調查,對于0.65 mm的封裝到封裝互連間距,一些顧客已經將翹曲目標降低到60μm。

PoP堆疊芯片清洗:PoP堆疊芯片/Sip系統級封裝在mm級別間距進行焊接,助焊劑作用后留下的活性劑等吸濕性物質,較小的層間距如存有少量的吸濕性活性劑足以占據相對較大的芯片空間,影響芯片可靠性。要將有限的空間里將殘留物帶離清除,清洗劑需要具備較低的表面張力滲入層間芯片,達到將殘留帶離的目的。合明科技研發的清洗劑具有卓越的滲入能力,以確保芯片間殘留活性劑被徹底清除。

合明科技為您提供PoP堆疊芯片水基清洗全工藝解決方案。

針對先進封裝產品芯片焊后封裝前,基板載板焊盤、電子制程精密焊后清洗的不同要求,合明科技在水基清洗方面有比較豐富的經驗,對于有著低表面張力、低離子殘留、配合不同清洗工藝使用的情況,自主開發了較為完整的水基系列產品,精細化對應涵蓋從半導體封裝到PCBA組件終端,包括有水基清洗劑和半水基清洗劑,堿性水基清洗劑和中性水基清洗劑等。具體表現在,在同等的清洗力的情況下,合明科技的兼容性較佳,兼容的材料更為廣泛;在同等的兼容性下,合明科技的清洗劑清洗的錫膏種類更多(測試過的錫膏品種有ALPHA、SMIC、INDIUM、SUPER-FLEX、URA、TONGFANG、JISSYU、HANDA、OFT、WTO等品牌;測試過的焊料合金包括SAC305、SAC307、6337、925等不同成分),清洗速度更快,離子殘留低、干凈度更好。

想了解更多關于先進封裝產品芯片清洗的內容,請訪問我們的“先進封裝產品芯片清洗”產品與應用!

合明科技運用自身原創的產品技術,滿足芯片封裝工藝制程清洗的高難度技術要求,打破國外廠商在行業中的壟斷地位,為芯片封裝材料全面國產自主提供強有力的支持。

推薦使用合明科技水基清洗劑產品。

![[x]](/template/default/picture/closeimgfz1.svg)