因?yàn)閷I(yè)

所以領(lǐng)先

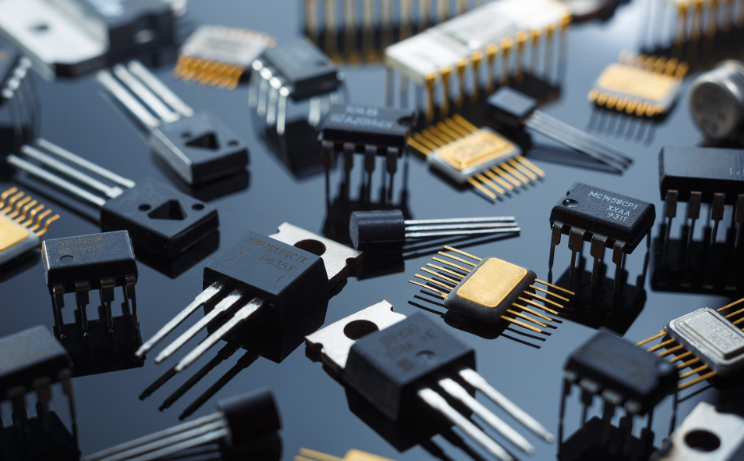

人工智能芯片的封裝是一個(gè)復(fù)雜的過(guò)程,涉及到多個(gè)技術(shù)層面的挑戰(zhàn)。以下是根據(jù)給定的搜索結(jié)果總結(jié)的三個(gè)關(guān)鍵挑戰(zhàn):

硅通孔(TSV)技術(shù)是2.5DIC封裝中的關(guān)鍵技術(shù)之一,它允許在芯片堆疊中實(shí)現(xiàn)垂直電氣通路。TSV具有極小的臨界尺寸、高縱橫比和精細(xì)螺距,可以實(shí)現(xiàn)大量的輸入/輸出。然而,TSV的制造過(guò)程非常密集,需要精確控制尺寸和深度,以及發(fā)現(xiàn)隱藏的缺陷。這些挑戰(zhàn)包括:

尺寸和深度控制:確保TSV的精確尺寸和深度對(duì)于保持高成品率至關(guān)重要。

電性能影響:TSV的制造質(zhì)量直接影響堆疊芯片之間的電性能。

制造步驟:包括蝕刻、沉積、填充和化學(xué)機(jī)械平坦化(CMP),這些步驟需要精確控制以避免缺陷。

微凸塊技術(shù)用于連接HBM堆棧內(nèi)的各個(gè)DRAM層和邏輯緩沖器芯片,以及將3D內(nèi)存堆棧和GPU連接到中介層。微凸塊的挑戰(zhàn)包括:

均勻性控制:保持凸塊電鍍的均勻性,無(wú)論是芯片內(nèi)還是整個(gè)晶圓上,都是一個(gè)挑戰(zhàn)。

厚度測(cè)量:測(cè)量用于構(gòu)造凸塊的每個(gè)金屬膜的單獨(dú)厚度對(duì)于控制器件的性能和可靠性至關(guān)重要。

缺陷檢測(cè):殘留物、裂紋、空隙的存在,或者微凸塊被損壞或移位,都可能導(dǎo)致設(shè)備故障。

隨著輸入/輸出(I/O)密度的增加,單個(gè)組件直接與印刷電路板配合的能力成為一個(gè)問(wèn)題。AICS作為軟件包各個(gè)組件之間的橋梁,其挑戰(zhàn)包括:

重疊錯(cuò)誤:隨著RDL層數(shù)的增加,重疊錯(cuò)誤的可能性也隨之增加。

互連技術(shù)要求:更精細(xì)的L/S要求增加了設(shè)計(jì)困境,需要增加RDL層的數(shù)量,同時(shí)增加成本和潛在的良率損失。

對(duì)準(zhǔn)解決方案:需要準(zhǔn)確的計(jì)量數(shù)據(jù)來(lái)生成最佳的對(duì)準(zhǔn)解決方案。

這些挑戰(zhàn)反映了人工智能芯片在先進(jìn)封裝過(guò)程中所面臨的復(fù)雜性和精細(xì)度要求。解決這些問(wèn)題需要先進(jìn)的制造技術(shù)和精密的控制方法,以確保芯片的性能和可靠性。

![[x]](/template/default/picture/closeimgfz1.svg)