因?yàn)閷I(yè)

所以領(lǐng)先

1.SoC原型驗(yàn)證:不可或缺的一環(huán)

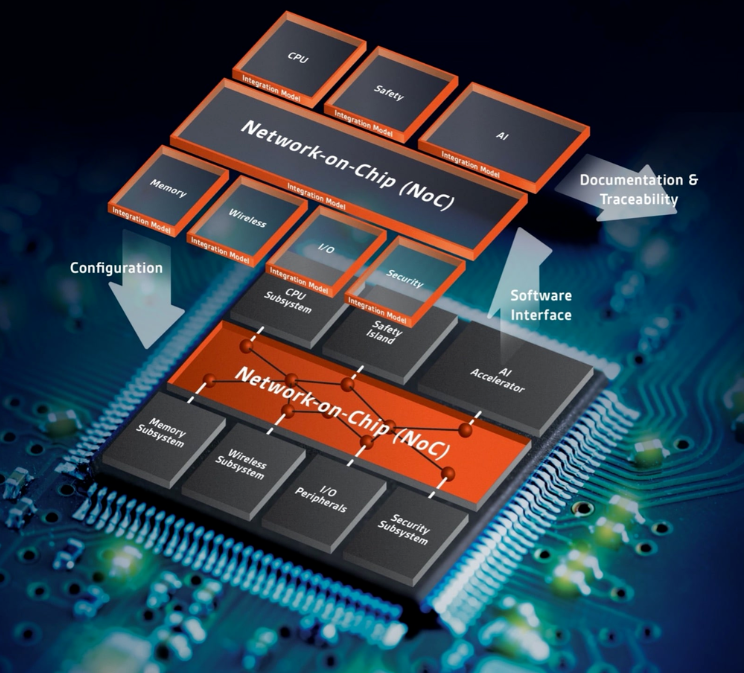

隨著AI、5G等尖端技術(shù)的進(jìn)步,“萬(wàn)物互聯(lián)”的愿景正逐步成為現(xiàn)實(shí),為人們帶來(lái)更便捷的生活方式,激發(fā)著無(wú)盡的應(yīng)用可能性。這不僅加速了芯片設(shè)計(jì)行業(yè)的變革,而且提出了更高的設(shè)計(jì)要求。摩爾定律表明,盡管芯片尺寸在縮小,但其上的晶體管數(shù)量正快速增長(zhǎng)。如此高的集成度要求更大規(guī)模的SoC(System-on-Chip)設(shè)計(jì),并對(duì)EDA工具的需求日增。

流片作為芯片設(shè)計(jì)成功的必經(jīng)階段,也是一個(gè)風(fēng)險(xiǎn)極高的過(guò)程。一個(gè)細(xì)小的設(shè)計(jì)失誤不僅可能導(dǎo)致昂貴的經(jīng)濟(jì)損失,還可能使整個(gè)產(chǎn)品錯(cuò)失市場(chǎng)窗口,給設(shè)計(jì)團(tuán)隊(duì)帶來(lái)巨大的挑戰(zhàn)。流片失敗的原因有很多,其中邏輯或功能上的錯(cuò)誤幾乎占所有因素的50%。而設(shè)計(jì)錯(cuò)誤又占整個(gè)功能缺陷的50%~70%,成工程師們的頭號(hào)大敵。因此,驗(yàn)證是SoC設(shè)計(jì)決定成敗的關(guān)鍵。但SoC驗(yàn)證極其復(fù)雜,約占整個(gè)研發(fā)時(shí)間的70%。想要縮減開(kāi)發(fā)周期,必須將系統(tǒng)軟件開(kāi)發(fā)驗(yàn)證和投片前驗(yàn)證并行,這使得原型驗(yàn)證的優(yōu)勢(shì)遠(yuǎn)超過(guò)其他。

對(duì)于大型SoC設(shè)計(jì),傳統(tǒng)的軟件仿真方法常常因運(yùn)行速度不足而成為瓶頸。于是,原型驗(yàn)證和硬件仿真成為兩大主流的驗(yàn)證手段,其中尤以原型驗(yàn)證因其高速性能而日益受到重視。與軟件仿真相比,原型驗(yàn)證的速度快數(shù)千至數(shù)百萬(wàn)倍,而與硬件仿真相比,原型驗(yàn)證成本更低,速度更快,成為可擴(kuò)展且經(jīng)濟(jì)有效的選擇,已經(jīng)成為驗(yàn)證復(fù)雜SoC必不可缺的EDA工具。

原型驗(yàn)證通常是基于FPGA(Field Programmable Gate Array,現(xiàn)場(chǎng)可編程門陣列)來(lái)實(shí)現(xiàn)的,因?yàn)镕PGA可構(gòu)造出和數(shù)字集成電路功能一樣的原型驗(yàn)證系統(tǒng),從而驗(yàn)證邏輯功能的正確性,成為前端驗(yàn)證的首選方法。過(guò)去,工程師們通常依賴手動(dòng)搭建的原型驗(yàn)證平臺(tái)。然而,這種方法在多FPGA和高度復(fù)雜的設(shè)計(jì)環(huán)境下變得難以維護(hù)和擴(kuò)展。其中手動(dòng)分割、邏輯分配以及多FPGA之間的接口設(shè)計(jì)是一個(gè)異常耗時(shí)且錯(cuò)誤率高的過(guò)程。在高度復(fù)雜的SoC設(shè)計(jì)中,單純依靠人工手段進(jìn)行原型驗(yàn)證難以保證項(xiàng)目的時(shí)效性和質(zhì)量。這種局限性不僅耗盡了大量的人力和物力,更增加了項(xiàng)目延期和成本超支的風(fēng)險(xiǎn)。面對(duì)這些挑戰(zhàn),才有了商業(yè)原型驗(yàn)證解決方案的誕生。

2.商用原型驗(yàn)證工具的誕生

1992年,Aptix公司——這家被視為原型驗(yàn)證工具的先驅(qū),推出了名為System Explorer的系統(tǒng),利用FPGA及自創(chuàng)的互聯(lián)芯片實(shí)現(xiàn)了商用原型驗(yàn)證工具。接下來(lái)的幾年,諸如多倫多大學(xué)的Transmogrifier-l、北卡州立大學(xué)的AnyBoard、斯坦福大學(xué)的Protozone以及加州大學(xué)圣克魯斯分校的BORG等項(xiàng)目,開(kāi)始探索如何在小型原型驗(yàn)證板上實(shí)現(xiàn)HDL芯片設(shè)計(jì)。

這些項(xiàng)目為后來(lái)的驗(yàn)證探索了多種可能性,盡管這些嘗試還未完全準(zhǔn)備好大規(guī)模商業(yè)化,但Aptix的成功給了其他供應(yīng)商很大的啟示,并激發(fā)了更多公司進(jìn)入這個(gè)領(lǐng)域。盡管Aptix公司如今已消失在之后的并購(gòu)浪潮中,但其在芯片驗(yàn)證方法學(xué)的開(kāi)創(chuàng)性貢獻(xiàn)仍然具有重要的歷史意義和價(jià)值。

2003年,林俊雄先生在EDA行業(yè)面臨重大變革之際,離開(kāi)了Aptix并創(chuàng)立了思爾芯(S2C)。這一大膽的決策預(yù)示著新時(shí)代的到來(lái)。[1]他選擇在美國(guó)硅谷的核心地區(qū)——加利福尼亞的圣何塞成立公司,并在第二年迅速在上海建立了總部和第一個(gè)研發(fā)中心。[2]當(dāng)時(shí)的中國(guó)在EDA領(lǐng)域還是一片荒漠,思爾芯集結(jié)了EDA精英,深耕中國(guó)這個(gè)巨大的潛在市場(chǎng)。不久便在2005年的DAC上推出了其首款原型驗(yàn)證產(chǎn)品,名為IP Porter,很快又迭代出了成熟可商用的Prodigy芯神瞳系列產(chǎn)品。

同一時(shí)期,在全球其他公司也開(kāi)始在原型驗(yàn)證領(lǐng)域探索。例如,美國(guó)的Dini Group在1998年推出了其第一款商業(yè)FPGA原型驗(yàn)證板,名為DN250k10。這款產(chǎn)品基于6顆Xilinx XC4085 FPGA,為芯片設(shè)計(jì)團(tuán)隊(duì)提供了一種靈活且經(jīng)濟(jì)實(shí)惠的解決方案。另一方面,瑞典的小企業(yè)HARDI Electronics AB在2000年也推出了基于Xilinx Virtex FPGA的首款原型驗(yàn)證系統(tǒng)——HAPS。但這些產(chǎn)品還需要工程師大量的手動(dòng)搭建原型驗(yàn)證環(huán)境。

3.迅猛發(fā)展源于EDA公司的激烈競(jìng)爭(zhēng)

2008年,美國(guó)公司 Synopsys以2.27億美元的價(jià)格兼并了Synplicity[3],進(jìn)入了原型驗(yàn)證市場(chǎng)。也代表了原型驗(yàn)證進(jìn)入了一個(gè)快速增長(zhǎng)且激烈競(jìng)爭(zhēng)的時(shí)代。Synopsys花了接近4年的時(shí)間才真正完成技術(shù)整合并發(fā)布了HAPS-70系列,是真正的自動(dòng)化原型驗(yàn)證產(chǎn)品。[4]之前的驗(yàn)證市場(chǎng)多以軟件仿真與硬件仿真為主,自Synopsys購(gòu)買之后,原型驗(yàn)證的市場(chǎng)正好飛速發(fā)展,成為主流必備的驗(yàn)證產(chǎn)品。

Cadence也參與其中。Cadence專注于設(shè)計(jì)自己的FPGA開(kāi)發(fā)板,但一直做得并不順利,直到Cadence在2010年3月收購(gòu)了Taray及其解決方案中的FPGA設(shè)計(jì)。因?yàn)門aray開(kāi)創(chuàng)了路由感知管腳分配綜合的先河,將其與電路板一起優(yōu)化了一個(gè)FPGA設(shè)計(jì),這將有助于設(shè)計(jì)一個(gè)原型驗(yàn)證平臺(tái)。有段時(shí)間,Cadence和Dini Group合作研發(fā)原型驗(yàn)證Protium產(chǎn)品。最終,Dini Group卻在2019年12月5日被“屢屢不夠”的Synopsys收購(gòu)[5]。如今的Cadence專注完善其原型驗(yàn)證產(chǎn)品和硬件仿真產(chǎn)品之間的銜接流程,實(shí)現(xiàn)兩者的快速相連。

西門子EDA(在2016年收購(gòu)了Mentor Graphics)在原型驗(yàn)證方面經(jīng)歷了一段曲折的歷程。該公司在1990年代末從Aptix獲得了仿真技術(shù)許可,但隨后遇到了一系列挑戰(zhàn),發(fā)展曾一度陷入停滯。之后,為了提升在原型驗(yàn)證中的時(shí)序驅(qū)動(dòng)和多FPGA分割能力,西門子EDA分別收購(gòu)了Auspy和法國(guó)的Flexras Technologies,后者擁有“Wasga自動(dòng)分割軟件”[6]。2021年6月西門子EDA又收購(gòu)了PRO DESIGN 的 proFPGA 產(chǎn)品系列[7],西門子EDA終于在原型驗(yàn)證領(lǐng)域?qū)崿F(xiàn)了產(chǎn)品和技術(shù)的全面加強(qiáng)。

除了一些EDA主要廠商,國(guó)內(nèi)一些較小型的供應(yīng)商也開(kāi)始提供低成本解決方案。國(guó)內(nèi)亞科鴻禹成立于2009年,原型驗(yàn)證產(chǎn)品為VeriTiger。另一家華桑電子2014年正式開(kāi)啟自有品牌PHINE Design系列原型驗(yàn)證產(chǎn)品的研發(fā)和銷售,至今已推出第四代產(chǎn)品。這些都是國(guó)內(nèi)較小供應(yīng)商,他們也在深耕這一領(lǐng)域,但整體來(lái)說(shuō)市場(chǎng)規(guī)模并不大。2020年后,在“國(guó)產(chǎn)化”的大背景下,又有新興公司如合見(jiàn)工軟,芯華章通過(guò)并購(gòu)和自研,快速進(jìn)入原型驗(yàn)證市場(chǎng)。

4.原型驗(yàn)證工具的幾大挑戰(zhàn)及解決方案

在三十多年的漫長(zhǎng)歲月中,原型驗(yàn)證技術(shù)實(shí)現(xiàn)了顯著的進(jìn)步。自從Aptix 的System Explorer產(chǎn)品亮相,原型驗(yàn)證就為芯片設(shè)計(jì)賦予了無(wú)與倫比的靈活性和效率。

隨著千禧年的到來(lái),硬件與軟件的深度定制帶來(lái)了原型驗(yàn)證的新挑戰(zhàn)與機(jī)遇,使其在芯片設(shè)計(jì)中的地位更加堅(jiān)固。隨后,國(guó)際上的三巨頭以及像思爾芯這樣的原型驗(yàn)證供應(yīng)商加入了戰(zhàn)局。他們通過(guò)策略性收購(gòu)和技術(shù)創(chuàng)新,使原型驗(yàn)證系統(tǒng)更加繁榮,滿足了市場(chǎng)的快速增長(zhǎng)。

面對(duì)芯片設(shè)計(jì)的日益增加的復(fù)雜性和對(duì)原型驗(yàn)證更為嚴(yán)格的要求,原型驗(yàn)證領(lǐng)域出現(xiàn)了許多創(chuàng)新解決方案。這個(gè)領(lǐng)域已經(jīng)變得越來(lái)越專業(yè)化,需要高度的專業(yè)知識(shí)和經(jīng)驗(yàn)來(lái)處理設(shè)計(jì)的分割、映射、與外部環(huán)境的接口與通信、調(diào)試及性能優(yōu)化等諸多問(wèn)題。因此,這也使得原型驗(yàn)證成為一個(gè)高壁壘的技術(shù)領(lǐng)域,僅有少數(shù)EDA公司能在這一領(lǐng)域保持領(lǐng)先地位,有些甚至需要不斷“并購(gòu)”才能夠在此領(lǐng)域占據(jù)領(lǐng)導(dǎo)地位的原因。

思爾芯作為原型驗(yàn)證領(lǐng)域的翹楚,對(duì)于多FPGA的RTL邏輯的分割、多片F(xiàn)PGA之間的互聯(lián)拓?fù)浣Y(jié)構(gòu)、IO分配以及高速接口等,推出了時(shí)序驅(qū)動(dòng)的RTL級(jí)分割算法和內(nèi)置的增量編譯算法功能來(lái)應(yīng)對(duì)這些問(wèn)題;也不斷推出新的硬件配置,例如支持更多的FPGA和提供更高的性能連接器,確保其技術(shù)始終處于行業(yè)前沿。還通過(guò)不斷的技術(shù)迭代和服務(wù)體系建設(shè),穩(wěn)定其在快速發(fā)展的市場(chǎng)中的地位,同時(shí)也提供了強(qiáng)大的供貨能力。

如今,思爾芯已積累了20年的產(chǎn)品和市場(chǎng)經(jīng)驗(yàn),成為中國(guó)最早涉足原型驗(yàn)證研究與銷售的領(lǐng)軍企業(yè),也是最早的國(guó)產(chǎn)數(shù)字EDA公司。根據(jù) CSIA 2020統(tǒng)計(jì),思爾芯原型驗(yàn)證方案中國(guó)市場(chǎng)份額超過(guò) 50%,在國(guó)內(nèi)排名第一。它可謂是接過(guò)了Aptix的接力棒,奔跑在中國(guó)原型驗(yàn)證的前沿,如今已穩(wěn)坐這一領(lǐng)域的寶座。近期,該公司成功發(fā)布了其第八代原型驗(yàn)證系統(tǒng)——芯神瞳S8-40。

在這些公司的共同努力之下,使得原型驗(yàn)證技術(shù)日趨成熟。不僅大大提高了當(dāng)今芯片設(shè)計(jì)的效率和質(zhì)量,還降低了整體芯片開(kāi)發(fā)成本。同時(shí),通過(guò)這些先進(jìn)技術(shù),設(shè)計(jì)團(tuán)隊(duì)能夠更靈活地應(yīng)對(duì)市場(chǎng)需求,從而保持競(jìng)爭(zhēng)力。可以說(shuō)原型驗(yàn)證技術(shù)的成熟和普及,為全球的芯片設(shè)計(jì)團(tuán)隊(duì)帶來(lái)了強(qiáng)大的支持和無(wú)數(shù)的便利,推動(dòng)了整個(gè)行業(yè)的持續(xù)發(fā)展。

5. 芯片封裝清洗:

合明科技研發(fā)的水基清洗劑配合合適的清洗工藝能為芯片封裝前提供潔凈的界面條件。

水基清洗的工藝和設(shè)備配置選擇對(duì)清洗精密器件尤其重要,一旦選定,就會(huì)作為一個(gè)長(zhǎng)期的使用和運(yùn)行方式。水基清洗劑必須滿足清洗、漂洗、干燥的全工藝流程。

污染物有多種,可歸納為離子型和非離子型兩大類。離子型污染物接觸到環(huán)境中的濕氣,通電后發(fā)生電化學(xué)遷移,形成樹(shù)枝狀結(jié)構(gòu)體,造成低電阻通路,破壞了電路板功能。非離子型污染物可穿透PC B 的絕緣層,在PCB板表層下生長(zhǎng)枝晶。除了離子型和非離子型污染物,還有粒狀污染物,例如焊料球、焊料槽內(nèi)的浮點(diǎn)、灰塵、塵埃等,這些污染物會(huì)導(dǎo)致焊點(diǎn)質(zhì)量降低、焊接時(shí)焊點(diǎn)拉尖、產(chǎn)生氣孔、短路等等多種不良現(xiàn)象。

這么多污染物,到底哪些才是最備受關(guān)注的呢?助焊劑或錫膏普遍應(yīng)用于回流焊和波峰焊工藝中,它們主要由溶劑、潤(rùn)濕劑、樹(shù)脂、緩蝕劑和活化劑等多種成分,焊后必然存在熱改性生成物,這些物質(zhì)在所有污染物中的占據(jù)主導(dǎo),從產(chǎn)品失效情況來(lái)而言,焊后殘余物是影響產(chǎn)品質(zhì)量最主要的影響因素,離子型殘留物易引起電遷移使絕緣電阻下降,松香樹(shù)脂殘留物易吸附灰塵或雜質(zhì)引發(fā)接觸電阻增大,嚴(yán)重者導(dǎo)致開(kāi)路失效,因此焊后必須進(jìn)行嚴(yán)格的清洗,才能保障電路板的質(zhì)量。

合明科技運(yùn)用自身原創(chuàng)的產(chǎn)品技術(shù),滿足芯片封裝工藝制程清洗的高難度技術(shù)要求,打破國(guó)外廠商在行業(yè)中的壟斷地位,為芯片封裝材料全面國(guó)產(chǎn)自主提供強(qiáng)有力的支持。

推薦使用合明科技水基清洗劑產(chǎn)品。

![[x]](/template/default/picture/closeimgfz1.svg)