因?yàn)閷?zhuān)業(yè)

所以領(lǐng)先

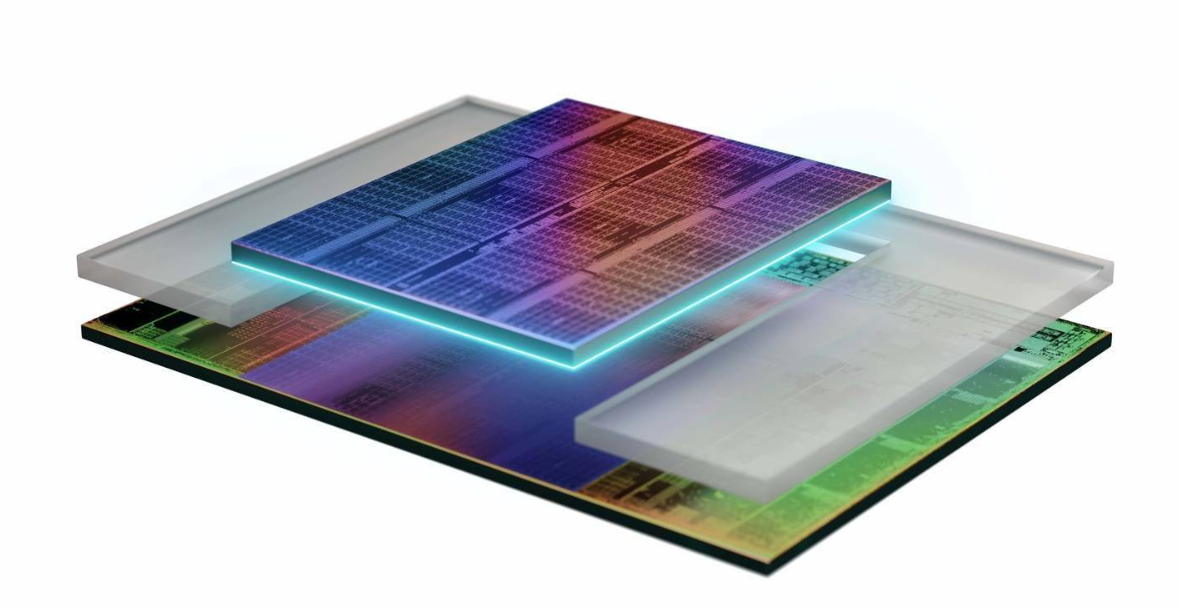

Chiplet晶圓混合鍵合技術(shù)是微電子封裝和先進(jìn)制造領(lǐng)域的一種新型連接技術(shù),在當(dāng)下已經(jīng)成為實(shí)現(xiàn)芯片堆疊以及未來(lái)3D封裝的一項(xiàng)關(guān)鍵技術(shù),是達(dá)成高性能、高密度芯片的重要手段 。

在當(dāng)前,半導(dǎo)體產(chǎn)業(yè)的發(fā)展對(duì)于國(guó)防安全和國(guó)民經(jīng)濟(jì)發(fā)展有著至關(guān)重要的意義,然而高端半導(dǎo)體裝備卻是國(guó)外對(duì)華技術(shù)封鎖的重點(diǎn)領(lǐng)域。盡管面臨這樣的困境,Chiplet晶圓混合鍵合技術(shù)依然在不斷發(fā)展。例如AMD在2021年宣布與臺(tái)積電合作開(kāi)發(fā)3D Chiplet,其3D Chiplet技術(shù)名為3D V - Cache,實(shí)現(xiàn)的關(guān)鍵技術(shù)包括硅通孔(TSV)和混合鍵合(Hybrid Bonding),并且首款采用該技術(shù)的產(chǎn)品Ryzen 7 5800X3D已經(jīng)問(wèn)世,這表明Chiplet晶圓混合鍵合技術(shù)已經(jīng)開(kāi)始在實(shí)際產(chǎn)品中得到應(yīng)用,并且展現(xiàn)出一定的技術(shù)成熟度,可以為芯片的性能提升帶來(lái)實(shí)際的效益,比如能夠在CPU上堆疊緩存,提高芯片的運(yùn)行效率等 。

此外,眾多企業(yè)和研究機(jī)構(gòu)也在積極探索該技術(shù)在不同場(chǎng)景下的應(yīng)用可能性,以提高芯片的集成度、降低功耗并提升整體性能。一些相關(guān)的技術(shù)標(biāo)準(zhǔn)和接口規(guī)范也在逐步建立,以促進(jìn)Chiplet晶圓混合鍵合技術(shù)在整個(gè)半導(dǎo)體行業(yè)的廣泛應(yīng)用。

Chiplet技術(shù)的概念最早可以追溯到2015年,Marvell創(chuàng)始人周秀文博士在2015年國(guó)際固態(tài)電路會(huì)議(ISSCC)上提出模塊化芯片概念,這是Chiplet最早的雛形 。

隨著半導(dǎo)體技術(shù)的發(fā)展,摩爾定律面臨失效的問(wèn)題,芯片制程的發(fā)展遇到瓶頸,傳統(tǒng)的單芯片設(shè)計(jì)方式在性能提升、成本控制等方面面臨挑戰(zhàn)。在這樣的背景下,Chiplet技術(shù)逐漸興起。芯原作為中國(guó)大陸第一,全球第七的半導(dǎo)體IP供應(yīng)商,在各類(lèi)處理器IP上有著深度布局,通過(guò)“IP芯片化(IP as a Chiplet)”和“芯片平臺(tái)化(Chiplet as a Platform)”持續(xù)推進(jìn)芯粒技術(shù)的發(fā)展和產(chǎn)業(yè)化落地,這也為Chiplet晶圓混合鍵合技術(shù)的發(fā)展奠定了一定的基礎(chǔ) 。

從封裝技術(shù)的發(fā)展來(lái)看,最初的多芯片模塊(MCM)封裝技術(shù)為Chiplet的發(fā)展提供了一定的思路,之后2.5D封裝和3D封裝技術(shù)不斷發(fā)展,這些技術(shù)提供更高的互連密度,可以集成更多芯片模塊,有助于提升芯片效能,降低系統(tǒng)功耗,而Chiplet晶圓混合鍵合技術(shù)則是在這些技術(shù)發(fā)展的基礎(chǔ)上進(jìn)一步發(fā)展起來(lái)的,是實(shí)現(xiàn)芯片更高性能、更高密度集成的關(guān)鍵技術(shù)之一,逐漸成為實(shí)現(xiàn)未來(lái)3D封裝的核心技術(shù)手段。

Chiplet晶圓混合鍵合技術(shù)要求極高的鍵合精度。在微觀層面,要實(shí)現(xiàn)晶圓與晶圓之間、芯片與芯片之間的精確連接并非易事。例如,在納米級(jí)別的工藝制程下,即使是微小的偏差也可能導(dǎo)致信號(hào)傳輸錯(cuò)誤或者電路功能異常。鍵合過(guò)程中的穩(wěn)定性也是一個(gè)關(guān)鍵問(wèn)題,任何微小的振動(dòng)、溫度變化或者化學(xué)物質(zhì)的干擾都可能影響鍵合的質(zhì)量,進(jìn)而影響整個(gè)芯片的性能和可靠性 。

在Chiplet技術(shù)中,可能會(huì)涉及到多種不同材料的芯片進(jìn)行混合鍵合。這些材料的物理和化學(xué)性質(zhì)各異,如熱膨脹系數(shù)、硬度、導(dǎo)電性等。當(dāng)它們組合在一起時(shí),如何確保在不同的工作環(huán)境(如溫度變化、電場(chǎng)作用等)下,各材料之間能夠穩(wěn)定地協(xié)同工作是一個(gè)挑戰(zhàn)。例如,硅基芯片與其他新型材料芯片(如III - V族化合物半導(dǎo)體芯片)混合鍵合時(shí),可能會(huì)因?yàn)椴牧闲再|(zhì)的差異而產(chǎn)生應(yīng)力,導(dǎo)致芯片出現(xiàn)裂縫或者性能下降。

開(kāi)發(fā)Chiplet晶圓混合鍵合技術(shù)需要投入大量的資金用于研發(fā)先進(jìn)的設(shè)備、工藝和材料。這些研發(fā)投入不僅包括硬件設(shè)施的建設(shè),還包括對(duì)專(zhuān)業(yè)技術(shù)人才的培養(yǎng)和引進(jìn)。例如,建立一套高精度的晶圓混合鍵合設(shè)備和研發(fā)相關(guān)的工藝技術(shù),需要耗費(fèi)巨額資金,并且研發(fā)周期較長(zhǎng),這對(duì)于企業(yè)來(lái)說(shuō)是一個(gè)巨大的成本壓力。

在實(shí)現(xiàn)技術(shù)突破之后,如何將Chiplet晶圓混合鍵合技術(shù)應(yīng)用于大規(guī)模生產(chǎn)并且實(shí)現(xiàn)成本的有效控制是另一個(gè)挑戰(zhàn)。要實(shí)現(xiàn)大規(guī)模生產(chǎn),需要解決設(shè)備的量產(chǎn)化、工藝的穩(wěn)定性和原材料的供應(yīng)等問(wèn)題。如果不能有效地控制成本,可能會(huì)導(dǎo)致采用Chiplet技術(shù)的芯片在市場(chǎng)上缺乏競(jìng)爭(zhēng)力,盡管其在性能上可能具有優(yōu)勢(shì)。

目前,Chiplet技術(shù)還缺乏統(tǒng)一的行業(yè)標(biāo)準(zhǔn),這對(duì)于晶圓混合鍵合技術(shù)的推廣和應(yīng)用帶來(lái)了很大的不便。不同的企業(yè)可能采用不同的設(shè)計(jì)規(guī)則、接口標(biāo)準(zhǔn)和鍵合工藝,這使得不同來(lái)源的Chiplet難以實(shí)現(xiàn)互操作性。例如,一家企業(yè)設(shè)計(jì)的Chiplet可能無(wú)法與另一家企業(yè)的芯片平臺(tái)進(jìn)行有效的混合鍵合和集成,這限制了Chiplet技術(shù)在整個(gè)行業(yè)的廣泛應(yīng)用。

Chiplet晶圓混合鍵合技術(shù)需要與現(xiàn)有的半導(dǎo)體技術(shù)和系統(tǒng)兼容。例如,在將Chiplet集成到現(xiàn)有的芯片架構(gòu)或者電路板設(shè)計(jì)中時(shí),可能會(huì)面臨信號(hào)匹配、電源管理和散熱等方面的問(wèn)題。如果不能很好地解決這些兼容性問(wèn)題,可能會(huì)導(dǎo)致整個(gè)系統(tǒng)的性能下降或者無(wú)法正常工作。

隨著人工智能(AI)、大數(shù)據(jù)、云計(jì)算等領(lǐng)域的快速發(fā)展,對(duì)于高性能計(jì)算芯片的需求日益增長(zhǎng)。Chiplet晶圓混合鍵合技術(shù)能夠?qū)⒉煌δ芎托阅艿男⌒酒M(jìn)行組合,實(shí)現(xiàn)高性能的異構(gòu)集成,從而滿(mǎn)足這些領(lǐng)域?qū)Ω邘挕⒏咚懔Α⒌脱訒r(shí)、低功耗的需求。例如,在AI訓(xùn)練和推理過(guò)程中,需要大量的計(jì)算資源,通過(guò)Chiplet技術(shù)可以將專(zhuān)門(mén)用于計(jì)算的芯片與存儲(chǔ)芯片等進(jìn)行高效集成,提高整個(gè)系統(tǒng)的計(jì)算效率 。

在物聯(lián)網(wǎng)(IoT)、車(chē)聯(lián)網(wǎng)、5G通信等多樣化的應(yīng)用場(chǎng)景中,對(duì)芯片的要求各不相同。Chiplet技術(shù)的靈活性使得制造商能夠根據(jù)不同的應(yīng)用需求定制芯片。例如,在車(chē)聯(lián)網(wǎng)場(chǎng)景中,可以將用于車(chē)輛控制、信息娛樂(lè)、自動(dòng)駕駛等不同功能的小芯片通過(guò)混合鍵合技術(shù)集成在一起,實(shí)現(xiàn)功能多樣化且性能優(yōu)化的芯片解決方案,滿(mǎn)足汽車(chē)電子系統(tǒng)對(duì)可靠性、低功耗和高性能的要求。

盡管Chiplet晶圓混合鍵合技術(shù)在理論上具有很大的優(yōu)勢(shì),但要實(shí)現(xiàn)商業(yè)化還面臨著諸多挑戰(zhàn)。如前面提到的技術(shù)層面的挑戰(zhàn)、成本與效益的平衡挑戰(zhàn)以及行業(yè)標(biāo)準(zhǔn)與兼容性挑戰(zhàn)等,這些都可能影響該技術(shù)在市場(chǎng)上的推廣和應(yīng)用。然而,一旦這些問(wèn)題得到解決,Chiplet技術(shù)有望在市場(chǎng)上取得巨大的成功,開(kāi)啟新的市場(chǎng)增長(zhǎng)點(diǎn)。

在Chiplet技術(shù)的市場(chǎng)發(fā)展過(guò)程中,競(jìng)爭(zhēng)與合作并存。一方面,眾多企業(yè)都在積極投入資源進(jìn)行Chiplet技術(shù)的研發(fā)和應(yīng)用,這將加劇市場(chǎng)競(jìng)爭(zhēng)。例如,半導(dǎo)體行業(yè)的各大巨頭都在探索如何利用Chiplet技術(shù)提升自己產(chǎn)品的競(jìng)爭(zhēng)力。另一方面,企業(yè)之間也存在合作的機(jī)會(huì),通過(guò)共享技術(shù)、資源和標(biāo)準(zhǔn),共同推動(dòng)Chiplet技術(shù)的發(fā)展。例如,芯片設(shè)計(jì)公司與封裝測(cè)試企業(yè)之間可以合作,發(fā)揮各自的優(yōu)勢(shì),加速Chiplet技術(shù)的產(chǎn)業(yè)化進(jìn)程。

在微觀層面進(jìn)一步提高鍵合工藝的精細(xì)化程度是一個(gè)重要的創(chuàng)新方向。例如,通過(guò)研發(fā)更先進(jìn)的光刻技術(shù)、蝕刻技術(shù)和沉積技術(shù)等,實(shí)現(xiàn)更小尺寸、更高精度的鍵合連接。這將有助于提高芯片的集成度,使得更多的小芯片能夠在有限的空間內(nèi)實(shí)現(xiàn)混合鍵合,從而提升芯片的整體性能。同時(shí),精細(xì)化的鍵合工藝還可以提高信號(hào)傳輸?shù)乃俣群头€(wěn)定性,減少信號(hào)延遲和干擾。

除了現(xiàn)有的鍵合材料和方法,探索新型的鍵合材料和方法也是創(chuàng)新的關(guān)鍵。例如,研究具有更好電學(xué)性能、熱性能和機(jī)械性能的新型材料,用于替代或補(bǔ)充現(xiàn)有的鍵合材料。此外,開(kāi)發(fā)新的鍵合方法,如基于分子間作用力或者量子效應(yīng)的鍵合方法,可能會(huì)為Chiplet晶圓混合鍵合技術(shù)帶來(lái)新的突破。這些新型鍵合材料和方法有望解決目前存在的材料兼容性、鍵合強(qiáng)度和穩(wěn)定性等問(wèn)題。

優(yōu)化異構(gòu)集成架構(gòu)是Chiplet技術(shù)創(chuàng)新的重要方向。通過(guò)對(duì)不同功能小芯片(如CPU、GPU、內(nèi)存芯片、IO芯片等)的合理布局和連接方式的創(chuàng)新,可以進(jìn)一步提高芯片的性能和能效比。例如,根據(jù)不同應(yīng)用場(chǎng)景下的計(jì)算需求,調(diào)整計(jì)算芯片和存儲(chǔ)芯片之間的距離和連接方式,減少數(shù)據(jù)傳輸?shù)木嚯x和延遲,提高數(shù)據(jù)處理的效率。同時(shí),還可以探索新的異構(gòu)集成架構(gòu)模式,如多層異構(gòu)集成架構(gòu),以實(shí)現(xiàn)更高的集成度和性能提升。

發(fā)展可重構(gòu)架構(gòu)也是一個(gè)有潛力的創(chuàng)新方向。可重構(gòu)架構(gòu)允許芯片在運(yùn)行過(guò)程中根據(jù)不同的任務(wù)需求動(dòng)態(tài)地調(diào)整其內(nèi)部結(jié)構(gòu)和功能。對(duì)于Chiplet晶圓混合鍵合技術(shù)來(lái)說(shuō),可以通過(guò)設(shè)計(jì)可重構(gòu)的小芯片和靈活的連接方式,實(shí)現(xiàn)芯片功能的動(dòng)態(tài)切換和優(yōu)化。例如,在一個(gè)既需要進(jìn)行圖形處理又需要進(jìn)行數(shù)據(jù)加密的應(yīng)用場(chǎng)景中,可重構(gòu)架構(gòu)的Chiplet芯片可以根據(jù)任務(wù)的優(yōu)先級(jí)和實(shí)時(shí)需求,動(dòng)態(tài)地調(diào)整GPU和加密芯片的工作模式和資源分配,提高芯片的利用率和性能。

建立統(tǒng)一的行業(yè)標(biāo)準(zhǔn)對(duì)于Chiplet晶圓混合鍵合技術(shù)的發(fā)展至關(guān)重要。這包括制定統(tǒng)一的設(shè)計(jì)規(guī)則、接口標(biāo)準(zhǔn)、鍵合工藝規(guī)范等。通過(guò)建立行業(yè)標(biāo)準(zhǔn),可以提高不同企業(yè)生產(chǎn)的Chiplet之間的互操作性,促進(jìn)Chiplet技術(shù)在整個(gè)行業(yè)的廣泛應(yīng)用。例如,制定統(tǒng)一的接口標(biāo)準(zhǔn)可以確保不同來(lái)源的小芯片能夠方便地進(jìn)行混合鍵合和集成,降低系統(tǒng)集成的難度和成本。

除了建立標(biāo)準(zhǔn),創(chuàng)新接口技術(shù)也是提高Chiplet技術(shù)性能的關(guān)鍵。例如,開(kāi)發(fā)高速、低功耗、高帶寬的接口技術(shù),可以提高小芯片之間的數(shù)據(jù)傳輸速度和效率。此外,研究具有自適應(yīng)性的接口技術(shù),能夠根據(jù)不同的工作環(huán)境和任務(wù)需求自動(dòng)調(diào)整接口參數(shù),進(jìn)一步提高接口的性能和兼容性。

· 合明科技研發(fā)的水基清洗劑配合合適的清洗工藝能為芯片封裝前提供潔凈的界面條件。

· 水基清洗的工藝和設(shè)備配置選擇對(duì)清洗精密器件尤其重要,一旦選定,就會(huì)作為一個(gè)長(zhǎng)期的使用和運(yùn)行方式。水基清洗劑必須滿(mǎn)足清洗、漂洗、干燥的全工藝流程。

· 污染物有多種,可歸納為離子型和非離子型兩大類(lèi)。離子型污染物接觸到環(huán)境中的濕氣,通電后發(fā)生電化學(xué)遷移,形成樹(shù)枝狀結(jié)構(gòu)體,造成低電阻通路,破壞了電路板功能。非離子型污染物可穿透PC B 的絕緣層,在PCB板表層下生長(zhǎng)枝晶。除了離子型和非離子型污染物,還有粒狀污染物,例如焊料球、焊料槽內(nèi)的浮點(diǎn)、灰塵、塵埃等,這些污染物會(huì)導(dǎo)致焊點(diǎn)質(zhì)量降低、焊接時(shí)焊點(diǎn)拉尖、產(chǎn)生氣孔、短路等等多種不良現(xiàn)象。

· 這么多污染物,到底哪些才是最備受關(guān)注的呢?助焊劑或錫膏普遍應(yīng)用于回流焊和波峰焊工藝中,它們主要由溶劑、潤(rùn)濕劑、樹(shù)脂、緩蝕劑和活化劑等多種成分,焊后必然存在熱改性生成物,這些物質(zhì)在所有污染物中的占據(jù)主導(dǎo),從產(chǎn)品失效情況來(lái)而言,焊后殘余物是影響產(chǎn)品質(zhì)量最主要的影響因素,離子型殘留物易引起電遷移使絕緣電阻下降,松香樹(shù)脂殘留物易吸附灰塵或雜質(zhì)引發(fā)接觸電阻增大,嚴(yán)重者導(dǎo)致開(kāi)路失效,因此焊后必須進(jìn)行嚴(yán)格的清洗,才能保障電路板的質(zhì)量。

· 合明科技運(yùn)用自身原創(chuàng)的產(chǎn)品技術(shù),滿(mǎn)足芯片封裝工藝制程清洗的高難度技術(shù)要求,打破國(guó)外廠商在行業(yè)中的壟斷地位,為芯片封裝材料全面國(guó)產(chǎn)自主提供強(qiáng)有力的支持。

![[x]](/template/default/picture/closeimgfz1.svg)