SIP系統級封裝工藝流程與技術

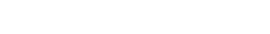

系統級封裝 (System in Package, SiP)是指將單個或多個芯片與各類元件通過系統設計及特定的封裝工藝集成于單一封裝體或模塊,從而實現具完整功能的電路集成,如圖所示。與系統級芯片 (SoC)常用于集成數字及邏輯電路不同,系統級封裝(SiP)更適用于無法(或非常困難)在單一芯片上實現功能集成的微波、射頻、功率等模擬電路的應用。

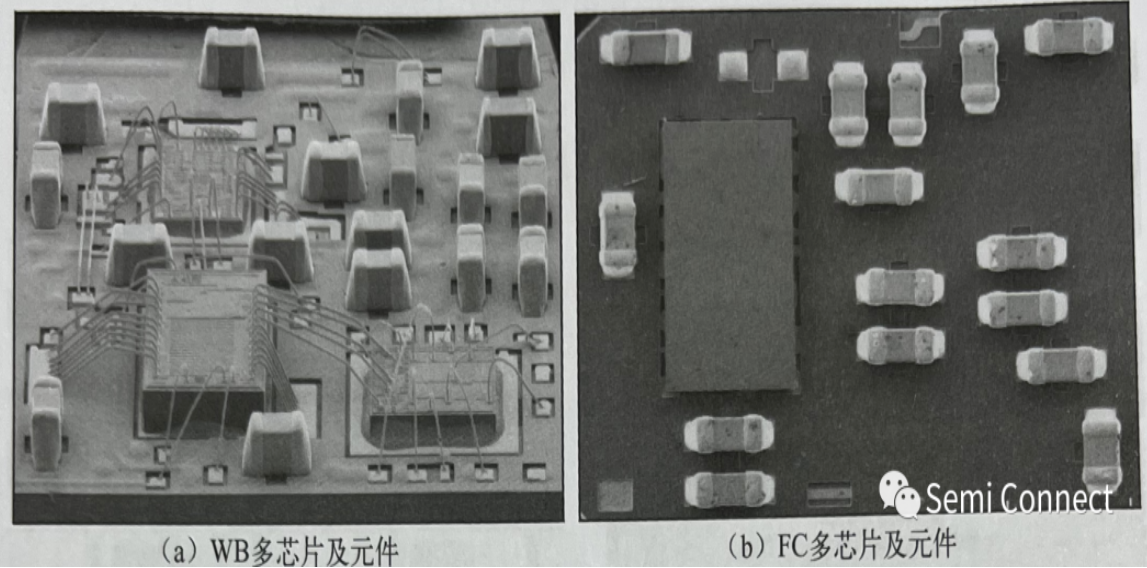

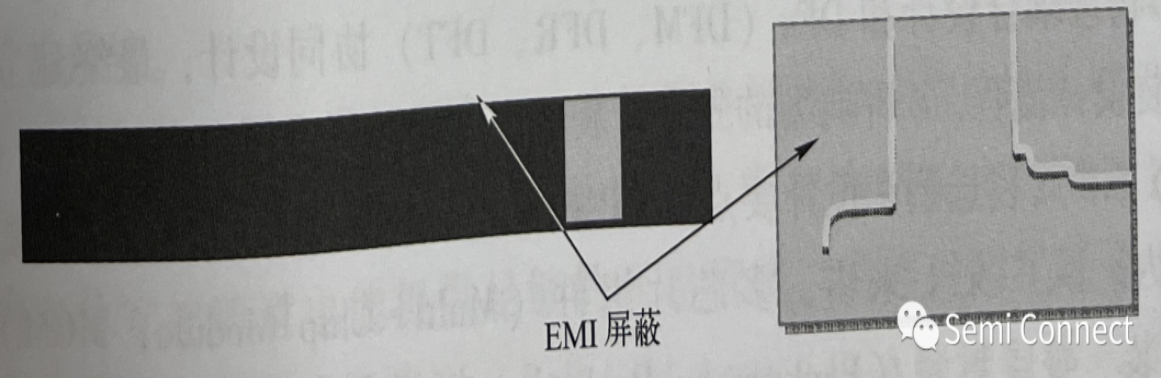

作為一種通過封裝工藝來實現集成電路產品的設計、開發和封測的主要技術和方法,SiP 并沒有固定的封裝形式和工藝,它可以在現有的大部分封裝類型上實現。通常,SiP 因為產品功能多樣化而選擇相對靈活的 LGA 設計如圖所示。但隨著該技術在更大、更復雜的系統電路中的迅速推廣,可以提供更多I/0 端口的 BGA 及整體化模塊也逐漸得以廣泛使用。另外,SiP 封裝模塊經常需要進行電磁屏蒰以消除模塊電路與環境之間的交互影響,而電磁屏蔽通常可以利用簡單的金屬蓋來實現。現在,高性能、高可靠性的 SiP 模塊也越來越多地使用塑封料包封加金屬涂層的工藝來實現電磁屏。

SiP 使用的基板和載體類型主要包括:薄膜厚膜及低溫燒結陶瓷(LTCC)基板;高密度的引線框基板;單層、多層及埋人式的有機基板;扇出型圓片級無基板再布線(RDL)連按等。

SiP 的主要封裝工藝方法和結構包括:多芯片SMT + WB/FC;芯片堆疊 SMT + WB/FC; 高密度3D/2.5D 封裝;疊層封裝(POP);扇出型圓片級SiP等。

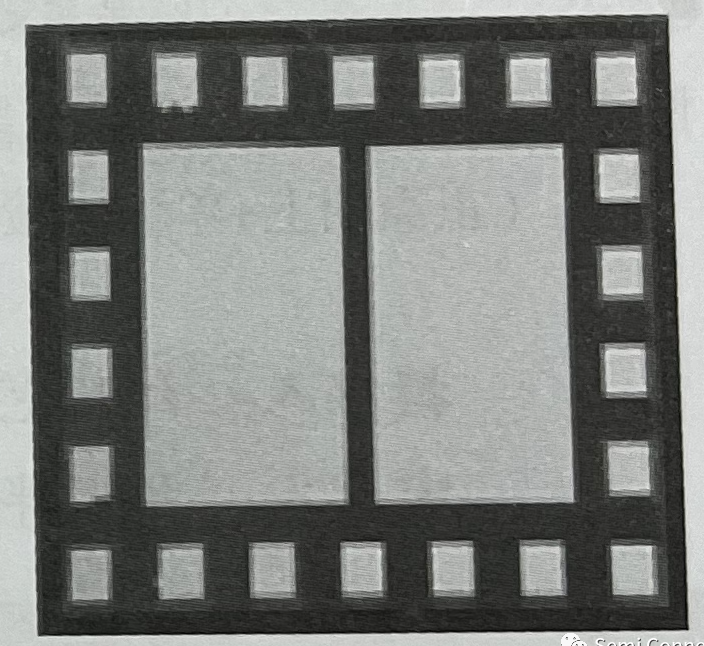

SiP 典型工藝流程如圖所示。由于 SiP涉及大量的多種類芯片和元器件,需要增加新的封裝工藝,如 SMT、電磁屏蔽濺射涂層等。雖然主要的半導體封裝工藝和設備可以共享,但 SP 工藝對這些通用封裝工藝也有很多特殊的新要求。

(1)高密度小間距表面貼裝:SiP 技術是推動元件及預封裝芯片 (WICSP、超薄超小CSP)尺寸微型化的最大驅動力,0201、01005區更小尺寸 008004 的電感、電容都是首先在 SiP 模塊中實現大批量使用的,先進的 WLCSP 的I/O間距小于 200μm,已接近 FC工藝。這些超小型元器件必須通過高速、高精度 SMT設備和工藝貼裝于 SiP 基板上,并通過錫膏及錫焊回流工藝實現連接。錫膏由錫焊顆粒和助焊劑均勻混合而成,錫焊合金成分、顆粒尺寸分布及助焊劑類型的選擇非常重要,通常應根據產品類型及工藝流程來確定。

(2)塑封:超小尺寸元器件及芯片,以區對應的高密度超小問距,有可能導致塑封料無法完全充分填充,從而造成可 靠性方面的隱患。通常的改善方法包括,優化塑封工藝參數,通過特殊的設計以增加塑封料的流動和填充,改變塑封料的固體顆粒的尺寸及分布,以及使用易于均勻填充的 Compresion 塑封工藝。

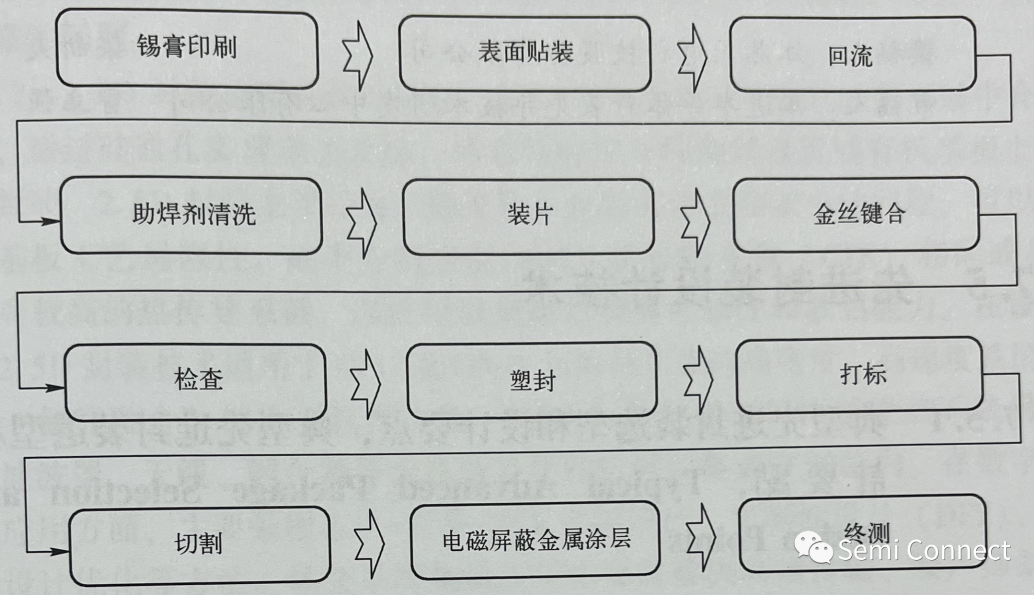

(3)電磁屏蔽金屬涂層:如圖所示,在塑封料表面形成電磁屏蔽金屬涂層是通過等離子濺射工藝或直按電鍍而實現的。因為工藝靈活,涂層結合力強,易于產能擴張,且不涉區濕法電化學所需要的廢水處理,等離子濺射金屬涂層已經逐步成為主流工藝。電磁屏蔽金屬涂層一般由多層金屬組成,從而保證金屬涂層與塑封料表面形成牢固的結合力。主層金屬常常選擇純銅,以利用其優異的導電性實現電磁干擾的屏蔽;外層金屬可以選擇不銹鋼,從而確保封裝體具有耐磨和良好的抗氧化性。為了形成完整的電磁屏蔽,金屬涂層必領實現上表面及四側面均覆蓋并按地。對于更高、更復雜的系統級封裝,也會使用分隔式電磁屏酸,從而進一步提高系統的整體電磁屏蔽效果。

【閱讀提示】

以上為本公司一些經驗的累積,因工藝問題內容廣泛,沒有面面俱到,只對常見問題作分析,隨著電子產業的不斷更新換代,新的工藝問題也不斷出現,本公司自成立以來不斷的追求產品的創新,做到與時俱進,熟悉各種生產復雜工藝,能為各種客戶提供全方位的工藝、設備、材料的清洗解決方案支持。

【免責聲明】

1. 以上文章內容僅供讀者參閱,具體操作應咨詢技術工程師等;

2. 內容為作者個人觀點, 并不代表本網站贊同其觀點和對其真實性負責,本網站只提供參考并不構成投資及應用建議。本網站上部分文章為轉載,并不用于商業目的,如有涉及侵權等,請及時告知我們,我們會盡快處理;

3. 除了“轉載”之文章,本網站所刊原創內容之著作權屬于合明科技網站所有,未經本站之同意或授權,任何人不得以任何形式重制、轉載、散布、引用、變更、播送或出版該內容之全部或局部,亦不得有其他任何違反本站著作權之行為。“轉載”的文章若要轉載,請先取得原文出處和作者的同意授權;

4. 本網站擁有對此聲明的最終解釋權。