高端性能封裝的結構解析與先進封裝芯片清洗

高性能計算、人工智能、5G 通信、數據中心和云計 算的快速發展使芯片的技術節點不斷向前推進,單顆 芯片上集成的晶體管數目已超過百億級。與此同時, 將更多功能集成在單顆芯片的難度不斷增大,設計與 制造的成本不斷上升。與 90 nm 技術節點相比,3 nm技術節點的投資成本增加了 35~40 倍,僅英特爾 (Intel)、臺積電(TSMC)和三星(Samsung)3 家頭部企 業參與其中。5 nm 技術節點的設計成本超過 5 億美 金,約是 28 nm 的 10 倍。為解決上述問題,出現了 Chiplet 概念。

Chiplet 作為一種設計概念,指將單顆集成復雜功 能的片上系統級芯片(SoC)離散成多顆特定功能的小 芯片(Chiplet,又稱“芯粒”),再采用封裝技術將其整合 在一起,構成多功能的異構系統級封裝(SiP),以持續 提高器件算力,縮短產品開發周期,提升產品良率,降 低整體成本。

高端性能封裝的結構

高端性能封裝主要以追求最優化計算性能為目的,其結構主要以 UHD FO、2.5D 和 3D 先進封裝為 主。在上述封裝結構中,決定封裝形式的主要因素為 價格、封裝密度和性能等。

由 TSMC 在先進封裝上的主要業務可知,推動高 端性能封裝的主要項目為高性能計算與高帶寬存儲, 其代表結構為基于硅轉接板的芯片在晶圓基板上的 封裝(CoWoS@-S),是一種典型的 2.5D 封裝結構。該 結構將處理芯片和存儲芯片平鋪在硅轉接板上,采用 線寬 / 線間距為 0.4 μm /0.4 μm 的金屬布線將其互 連。TSMC 突破光罩對硅轉接板面積的限制,結合集成 芯片的數量,制定了其在 2.5D 封裝上的發展路線。 Intel 和 Samsung 在 2.5D 封裝上,也具有類似的封裝結構。對于 2.5D 封裝而言,硅轉接板可提供亞微米 級高密度布線,能夠顯著提升多芯片的組裝密度。隨 著高帶寬存儲芯片的數據傳輸效率逐步提升,采用 2.5D 封裝連接存儲芯片和處理器芯片將成為主流的 選擇。然而,硅轉接板采用前道晶圓制造的設備和工 藝,制作成本相對昂貴。為此,一些企業在 FO 封裝的 基礎上進一步深耕,開發出多樣化的結構,以滿足一 些稍低端產品的需求。

FO 通過晶圓重構技術,將多顆相同或不同的芯 片靈活組合起來,以實現多芯片集成的目的。在此基 礎上,FO 采用高密度布線有機層、硅橋和高速基板等 來提升器件的性能,衍生出了 2D、2.1D、2.2D 和 2.3D 封裝結構,以實現超高密度 I/O 的連接。由于 FO 主要采用高分子材料來制造芯片間的微米級布線,其 自身的線寬 / 間距的尺寸極限也相對明顯。為進一步 縮小 FO 封裝的布線尺寸,新的設備與材料有待開發, 同時,封裝成本也將大大提高。因此,FO 封裝主要應 用在性能相對較低的存儲器與處理器芯片上。

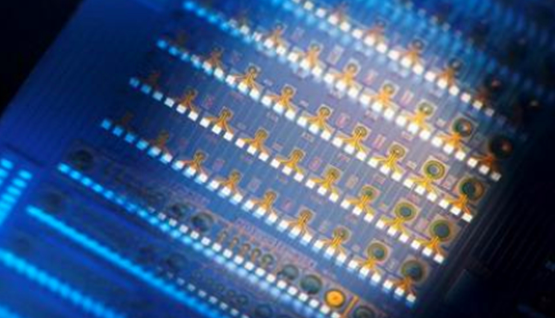

在高端性能封裝中,處理芯片和存儲芯片對高帶 寬、低延遲有嚴格的要求,3D 封裝是最理想的方案。目 前,常見的 3D 封裝結構為存儲芯片間垂直互連以及 存儲芯片與邏輯芯片間的連接。在上述結構中,除采 用微凸點的芯片堆疊(C2C)和晶圓上芯片(C2W)工藝 外,基于硅通孔和混合鍵合(HB)的無凸點工藝實現了 異構異質芯片間的最短距離互連,將器件性能提至最 優,其投資成本也最高。預計在 2023 年,TSMC 采 用 HB 的集成芯片系統封裝(SoIC)將率先實現量產。

隨著高端性能封裝技術的發展,不同維度封裝結 構間的界限將變得模糊,將其集合成一個系統的 SiP 會變得普遍,圖 1 為集成多維度封裝的 SiP 結構示意 圖。例如 Intel 的最新產品 Ponte Vecchio 集成了嵌入 式多芯片互連橋接技術(EMIB)和邏輯晶圓 3D 堆疊 技術(Foveros);TSMC 的 SoIC 也可與 CoWoS 和集成扇出型疊層封裝(InFO-PoP)相結合并共同使用。上述 結構可以實現器件對性能的極致追求,同時,多顆處 理芯片的集成也為器件的熱耗散帶來巨大挑戰。

先進封裝芯片清洗劑:

先進封裝產品芯片焊后封裝前,基板載板焊盤上的污染物有多種,可歸納為離子型和非離子型兩大類。離子型污染物接觸到環境中的濕氣,通電后發生電化學遷移,形成樹枝狀結構體,造成低電阻通路,破壞了電路板功能。非離子型污染物可穿透PC B 的絕緣層,在PCB板表層下生長枝晶。除了離子型和非離子型污染物,還有粒狀污染物,例如焊料球、焊料槽內的浮點、灰塵、塵埃等,這些污染物會導致焊點質量降低、焊接時焊點拉尖、產生氣孔、短路等等多種不良現象。

這么多污染物,到底哪些才是最備受關注的呢?助焊劑或錫膏普遍應用于回流焊和波峰焊工藝中,它們主要由溶劑、潤濕劑、樹脂、緩蝕劑和活化劑等多種成分,焊后必然存在熱改性生成物,這些物質在所有污染物中的占據主導,從產品失效情況來而言,焊后殘余物是影響產品質量最主要的影響因素,離子型殘留物易引起電遷移使絕緣電阻下降,松香樹脂殘留物易吸附灰塵或雜質引發接觸電阻增大,嚴重者導致開路失效,因此焊后必須進行嚴格的清洗,才能保障電路板的質量。

針對先進封裝產品芯片焊后封裝前,基板載板焊盤、電子制程精密焊后清洗的不同要求,合明科技在水基清洗方面有比較豐富的經驗,對于有著低表面張力、低離子殘留、配合不同清洗工藝使用的情況,自主開發了較為完整的水基系列產品,精細化對應涵蓋從半導體封裝到PCBA組件終端,包括有水基清洗劑和半水基清洗劑,堿性水基清洗劑和中性水基清洗劑等。具體表現在,在同等的清洗力的情況下,合明科技的兼容性較佳,兼容的材料更為廣泛;在同等的兼容性下,合明科技的清洗劑清洗的錫膏種類更多(測試過的錫膏品種有ALPHA、SMIC、INDIUM、SUPER-FLEX、URA、TONGFANG、JISSYU、HANDA、OFT、WTO等品牌;測試過的焊料合金包括SAC305、SAC307、6337、925等不同成分),清洗速度更快,離子殘留低、干凈度更好。

【閱讀提示】

以上為本公司一些經驗的累積,因工藝問題內容廣泛,沒有面面俱到,只對常見問題作分析,隨著電子產業的不斷更新換代,新的工藝問題也不斷出現,本公司自成立以來不斷的追求產品的創新,做到與時俱進,熟悉各種生產復雜工藝,能為各種客戶提供全方位的工藝、設備、材料的清洗解決方案支持。

【免責聲明】

1. 以上文章內容僅供讀者參閱,具體操作應咨詢技術工程師等;

2. 內容為作者個人觀點, 并不代表本網站贊同其觀點和對其真實性負責,本網站只提供參考并不構成投資及應用建議。本網站上部分文章為轉載,并不用于商業目的,如有涉及侵權等,請及時告知我們,我們會盡快處理;

3. 除了“轉載”之文章,本網站所刊原創內容之著作權屬于合明科技網站所有,未經本站之同意或授權,任何人不得以任何形式重制、轉載、散布、引用、變更、播送或出版該內容之全部或局部,亦不得有其他任何違反本站著作權之行為。“轉載”的文章若要轉載,請先取得原文出處和作者的同意授權;

4. 本網站擁有對此聲明的最終解釋權。