因為專業

所以領先

所謂芯片尺寸封裝就是CSP (Chip Size Package或Chip Scale Package)。JEDEC(美國EIA協會聯合電子器件工程委員會)的JSTK一012標準規定,LSI芯片封裝面積小于或等于LSI芯片面積的120%的產品稱之為CSP。CSP技術的出現確保VLSI在高性能、高可靠性的前提下實現芯片的最小尺寸封裝(接近裸芯片的尺寸),而相對成本卻更低,因此符合電子產品小型化的發展潮流,是極具市場競爭力的高密度封裝形式。本文從CSP的特點、類別和制作上藝以及生產和研發等幾個方面詳細論述這種先進的封裝技術,并對我國CSP技術的研發提出幾點建議。

一、 CSP的特點

CSP實際上是在BGA封裝小型化過程中形成的,所以有人也將CSP稱之為μBGA(微型球柵陣列,現在僅將它劃為CSP的一種形式),因此它自然地具有BGA封裝技術的許多優點。

1、 封裝尺寸小

CSP是目前體積最小的VLSI封裝之一。一般,CSP封裝面積不到0.5 mm,而間距是QFP的1/10,BGA的1/3~l/10。

2、 可容納引腳的數最多

在各種相同尺寸的芯片封裝中,CSP可容納的引腳數最多,適宜進行多引腳數封裝,甚至可以應用在I/0數超過2000的高性能芯片上。例如,引腳間距為0.5 mm,封裝尺寸為40 mm×40 mm的QFP,引腳數最多為304根,若要增加引腳數,只能減小引腳間距,但在傳統工藝條件下,OFP難以突破0.3 mm的技術極限;與CSP相提并論的是BGA封裝,它的引腳數可達600~1000根,但值得重視的是,在引腳數相同的情況下,CSP的組裝遠比BGA容易。

3、 電性能優良

CSP的內部布線長度(僅為0.8~1.O mm)比QFP或BGA的布線長度短得多,寄生引線電容、引線電阻及引線電感均很小,從而使信號傳輸延遲大為縮短。CSP的存取時間比QFP或BGA短1/5~1/6左右,同時CSP的抗噪能力強,開關噪聲只有DIP(雙列直插式封裝)的1/2。這些主要電學性能指標已經接近裸芯片的水平,在時鐘頻率己超過雙G的高速通信領域,LSI芯片的CSP將是十分理想的選擇。

4 、測試、篩選、老化操作容易實現

MCM技術是當今最高效、最先進的高密度封裝之一,其技術核心是采用裸芯片安裝,優點是無內部芯片封裝延遲及大幅度提高了組件封裝密度,因此未來市場令人樂觀。但它的裸芯片測試、篩選、老化問題至今尚未解決,合格裸芯片的獲得比較困難,導致成品率相當低,制造成本很高;而CSP則可進行全面老化、篩選、測試,并且操作、修整方便,能獲得真正的KGD芯片,在目前情況下用CSP替代裸:芯片安裝勢在必行。

5、 散熱性能優良

CSP封裝通過焊球與PCB連接,由于接觸面積大,所以芯片在運行時所產生的熱量可以很容易地傳導到PCB上并散發出去;而傳統的TSOP(薄型小外形封裝)方式中,芯片是通過引腳焊在PCB上,焊點和PCB板的接觸面積小,使芯片向PCB板散熱相對困難。測試結果表明,通過傳導方式的散熱量可占到80%以上。同時,CSP芯片正面向下安裝,可以從背面散熱,且散熱效果良好。例如松下電子開發的10 mm×10mm CSP的熱阻為35℃/W,而TSOP、QFP的熱阻則可達40℃/W。若通過散熱片強制冷卻,CSP的熱阻可降低到4.2℃/W,而QFP的則為11.8℃/W。

6、 封裝內無需填料

大多數CSP封裝中凸點和熱塑性粘合劑的彈性很好,不會因晶片與基底熱膨脹系數不同而造成應力,因此也就不必在底部填料,省去了填料時間和填料費用,這在傳統的SMT封裝中是不可能的。

7、 制造工藝、設備的兼容性好

CSP與現有的SMT工藝和基礎設備的兼容性好,而且它的引腳間距完全符合當前使用的SMT標準(0.5~1 mm),無需對PCB進行專門設計,而且組裝容易,因此完全可以利用現有的半導體工藝設備、組裝技術組織生產。

二、 CSP的分類

目前全球有50多家IC廠商生產各種結構的CSP產品。根據目前各廠商的開發情況,可將CSP封裝分為下列主要類別:

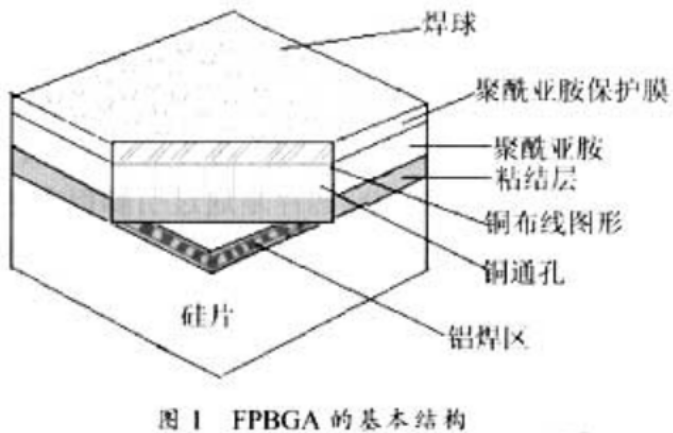

(1)柔性基板封裝CSP。柔性基板封裝CSP是由日本的NEC公司利用TAB技術研制開發出來的一種窄間距的BGA,因此也可以稱之為FPBGA。這類CSP封裝的基本結構如圖1所示,

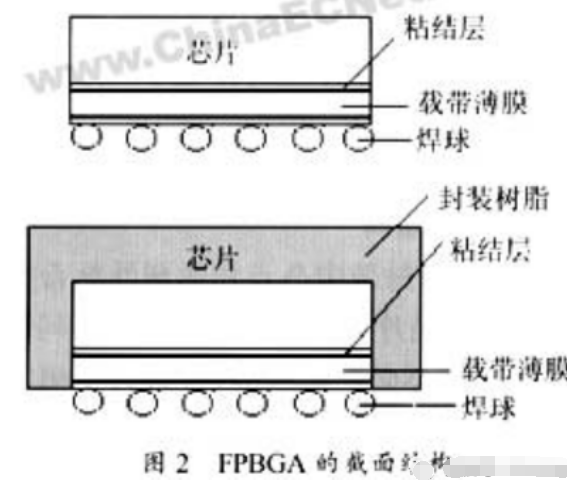

截面結構如圖2所示。

主要由IC芯片、載帶(柔性體)、粘接層、凸點(銅/鎳)等構成。載帶是用聚酰亞胺和制箔組成。采用共晶焊料(63%Sn一37%Pb)作外部互連電極材料。

其主要特點是結構簡單,可靠性高,安裝方便,可利用傳統的TAB(Tape Automated Bonding)焊接機進行焊接。

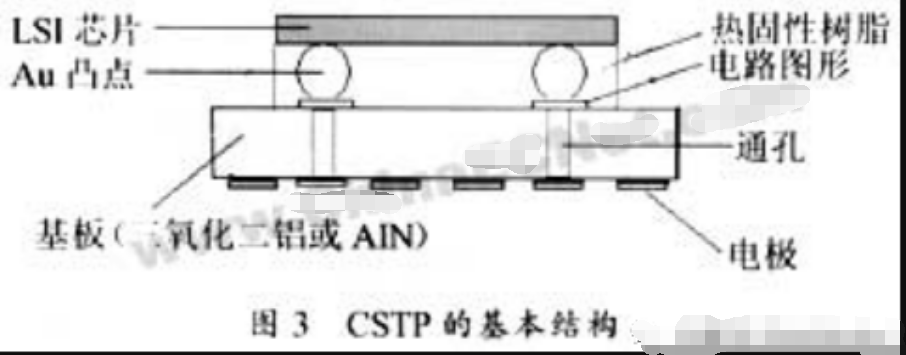

(2)剛性基板CSP。剛性基板CSP是由日本的Toshiba公司開發的一種陶瓷基板超薄型封裝,因此又可稱之為陶瓷基板薄形封裝CSTP(Ceramic Substrate Thin Package)。其基本結構見圖3。它主要由芯片、氧化鋁(Al2O3)基板、銅(Au)凸點和樹脂構成。通過倒裝焊、樹脂填充和打印3個步驟完成。它的封裝效率(芯片與基板面積之比)可達到75%,是相同尺寸的TQFP的2.5倍。

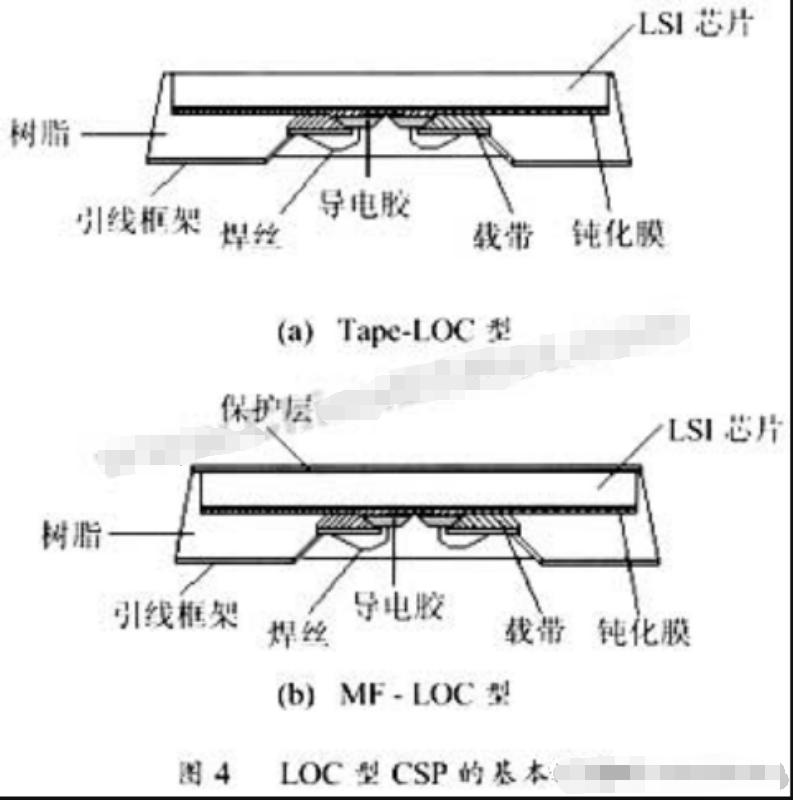

(3)引線框架式CSP。引線框架式CSP是由日本的Fujitsu公司研制開發的一種芯片上引線的封裝形式,因此也被稱之為LOC(Lead On Chip)形CSP。通常情況下分為Tape-LOC型和MF- LOC型(Mul-ti-frame-LOC)兩種形式,其基本結構如圖4所示。

由圖可知,這兩種形式的LOC形CSP都是將LSI芯片安裝在引線框架上,芯片面朝下,芯片下面的引線框架仍然作為外引腳暴露在封裝結構的外面。因此,不需要制作工藝復雜的焊料凸點,可實現芯片與外部的互連,并且其內部布線很短,僅為0.1 mm左右。

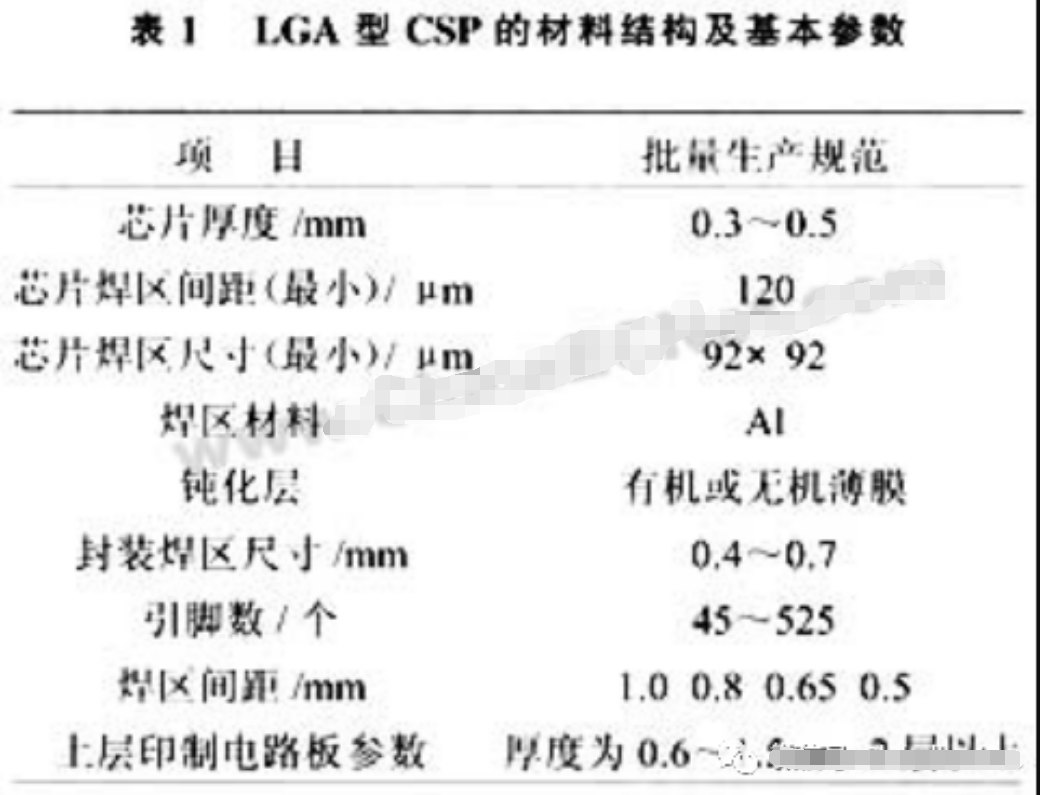

(4)焊區陣列CSP。焊區陣列CSP是由日本的Panasonic公司研制開發的一種新型封裝形式,也被稱之為LGA(Land Grid Array)型CSP,主要由LSI芯片、陶瓷載體、填充用環氧樹脂和導電粘結劑等組成。這種封裝的制作工藝是先用金絲打球法在芯片的焊接區上形成Au凸點,然后在倒裝焊時,在基板的焊區上印制導電膠,之后對事先做好的凸點加壓,同時固化導電膠,這就完成了芯片與基板的連接。導電膠由Pd-Ag與特殊的環氧樹脂組成,固化后保持一定彈性,因此,即使承受一定的應力,也不易受損。表1示出了其材料結構與一些基本參數。

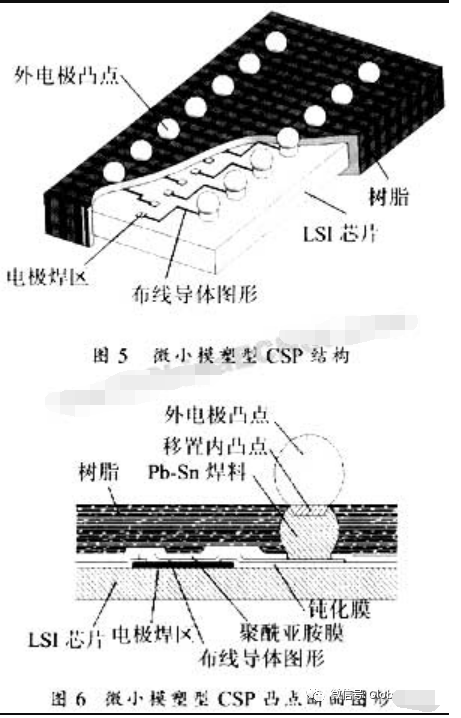

(5)微小模塑型CSP。微小模塑型CSP是由日本三菱電機公司研制開發出來的一種新型封裝形式。它主要由IC芯片、模塑的樹脂和凸點等構成。芯片上的焊區通過在芯片上的金屬布線與凸點實現互連,整個芯片澆鑄在樹脂上,只留下外部觸點。這種結構可實現很高的引腳數,有利于提高芯片的電學性能、減少封裝尺寸、提高可靠性,完全可以滿足儲存器、高頻器件和邏輯器件的高I/O數需求。同時由于它無引線框架和焊絲等,體積特別小,提高了封裝效率。基本結構如圖5所示,凸點斷面圖形如圖6所示。

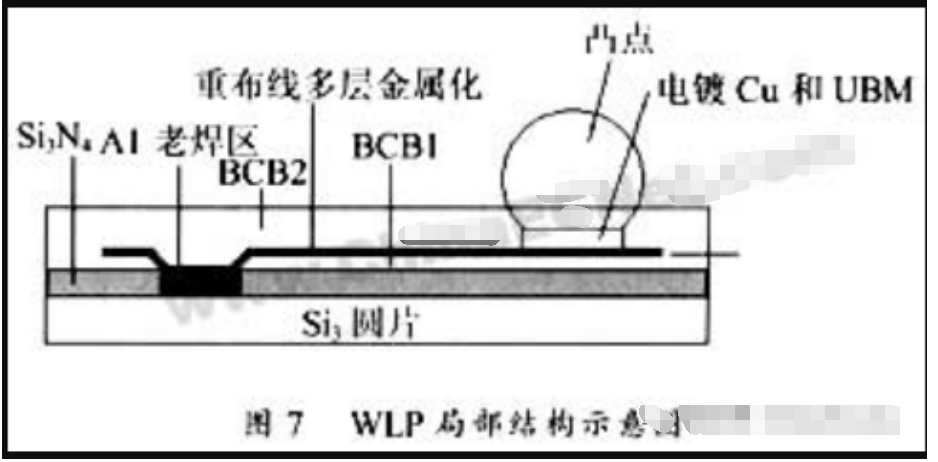

微小模塑型CSP的制作工藝:首先在LSI芯片上制作連接焊區和外引腳的金屬布線圖形,制出Pb-Sn焊料浸潤性良好的底層金屬,制出聚酰亞胺緩沖層,在聚酰亞胺開口區域采用蒸發光刻方法形成Pb-Sn層;然后,將上述經過再布線的芯片到裝焊在易于移植金凸點的框架上,使之于芯片焊區一一對應,加熱加壓,Pb-Sn熔化后就使框架上的金屬凸點(一般為Cu)移植到芯片上;最后,模塑封裝,脫模去除毛刺,形成外電極焊球。(6)圓片級CSP。圓片級CSP封裝(Wafer一Level Package)由ChipScale公司開發的此類封裝見圖5。它是在圓片前道工序完成后,直接對圓片利用半導體工藝進行后續組件封裝,利用劃片槽構造周邊互連,再切割分離成單個器件。WLP主要包括兩項關鍵技術即再分布技術和凸焊點制作技術。它有以下特點:①相當于裸片大小的小型組件(在最后工序切割分片);②以圓片為單位的加工成本(圓片成本率同步成本);③加工精度高(由于圓片的平坦性、精度的穩定性)。圓片級CSP的局部結構示意圖如圖7所示。

與其他各類CSP相比,圓片級CSP只是在IC工藝線上增加了重布線和凸點制作兩部分,并使用了兩層BCB和PI作為介質和保護層,所使用的工藝仍是傳統的金屬淀積、光刻、蝕刻技術,最后也無需模塑或底部下填充其他材料。圓片級CSP從晶圓片開始到做出器件,整個工藝流程一起完成,并可利用現有的標準SMT設備,生產計劃和生產的組織可以做到最優化;硅加工工藝和封裝測試可以在硅片生產線上進行而不必把晶圓送到別的地方去進行封裝測試;測試可以在切割CSP封裝產品之前一次完成,因而節省了測試的開支。總之,WLP成為未來CSP的主流已是大勢所驅。

除以上列舉的幾類封裝結構外,還有許多符合CSP定義的封裝結構形式這里就不再贅述。

三、先進芯片尺寸封裝(CSP)清洗:

合明科技研發的水基清洗劑配合合適的清洗工藝能為芯片封裝前提供潔凈的界面條件。

水基清洗的工藝和設備配置選擇對清洗精密器件尤其重要,一旦選定,就會作為一個長期的使用和運行方式。水基清洗劑必須滿足清洗、漂洗、干燥的全工藝流程。

污染物有多種,可歸納為離子型和非離子型兩大類。離子型污染物接觸到環境中的濕氣,通電后發生電化學遷移,形成樹枝狀結構體,造成低電阻通路,破壞了電路板功能。非離子型污染物可穿透PC B 的絕緣層,在PCB板表層下生長枝晶。除了離子型和非離子型污染物,還有粒狀污染物,例如焊料球、焊料槽內的浮點、灰塵、塵埃等,這些污染物會導致焊點質量降低、焊接時焊點拉尖、產生氣孔、短路等等多種不良現象。

這么多污染物,到底哪些才是最備受關注的呢?助焊劑或錫膏普遍應用于回流焊和波峰焊工藝中,它們主要由溶劑、潤濕劑、樹脂、緩蝕劑和活化劑等多種成分,焊后必然存在熱改性生成物,這些物質在所有污染物中的占據主導,從產品失效情況來而言,焊后殘余物是影響產品質量最主要的影響因素,離子型殘留物易引起電遷移使絕緣電阻下降,松香樹脂殘留物易吸附灰塵或雜質引發接觸電阻增大,嚴重者導致開路失效,因此焊后必須進行嚴格的清洗,才能保障電路板的質量。

合明科技運用自身原創的產品技術,滿足芯片封裝工藝制程清洗的高難度技術要求,打破國外廠商在行業中的壟斷地位,為芯片封裝材料全面國產自主提供強有力的支持。

推薦使用合明科技水基清洗劑產品。

![[x]](/template/default/picture/closeimgfz1.svg)