基板封裝材料選擇與先進封裝基板清洗劑介紹

發布日期:2023-06-26

發布者:合明科技

瀏覽次數:4220

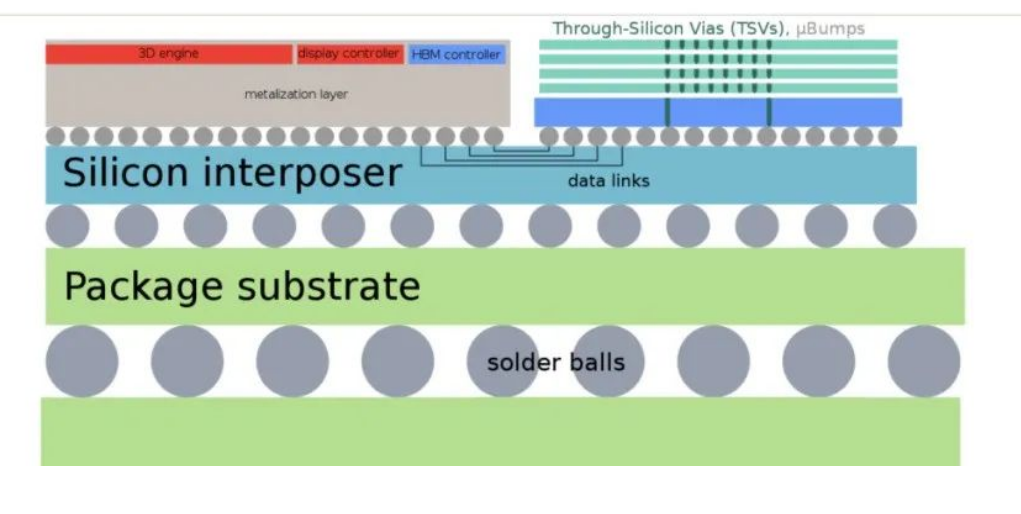

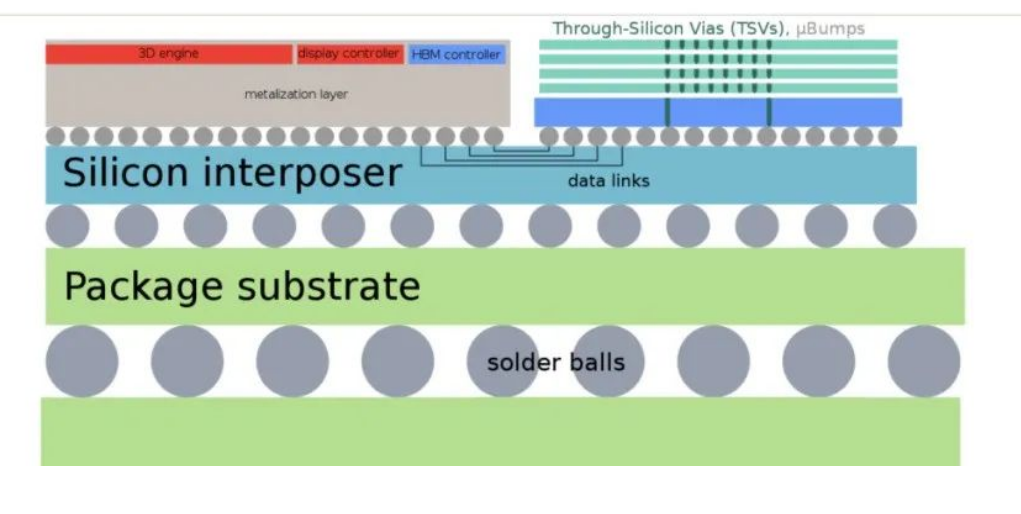

在封裝內集成更多數量的有源電路是一種通過密集互連將不同功能分配到集成到同一封裝中的不同芯片的方法。制造基于小芯片的產品,您需要設計技能、裸片、裸片之間的連接以及生產策略。chiplet封裝技術的性能、價格和成熟度對chiplet的應用有著實質性的影響。根據連接介質和方式的不同,用于chiplet互連的封裝技術可分為三類:基板封裝(Substrate packaging)、硅中介層封裝(Silicon-interposer packaging)、再分布層 (RDL:Redistribution-layer ) 封裝以及嵌入式多芯片互連橋 (EMIB:Embedded multi-die interconnect bridge )。首先看基板封裝。流行的基板選擇是有機材料,因為這些材料很容易獲得。與傳統 PCB 類似,布線連接是通過蝕刻工藝完成的,該工藝獨立于半導體制造中使用的其他工藝。這是最著名的 2D 異構集成的最早化身。通過倒裝芯片設計或堆疊,可以輕松地將多個裸片高密度地連接到基板上。此外,與之相關的材料和制造成本極低,因為該技術不依賴于芯片制造工藝。使用這種技術的主要缺點是 I/O 引腳密度低,從而限制了這些封裝中互連的帶寬。其次看硅中介層封裝,該技術涵蓋 2.5D 和 3D 封裝技術,芯片在中介層上橫向構建 (2.5D) 或垂直堆疊 (3D)。為了實現裸片之間的互連和通信,將硅中介層放置在基板和裸片之間。中介層就像一個微型印刷電路板,本質上是為小芯片之間的電連接提供基板。互連結構由金屬觸點(稱為微凸塊)和在封裝內部運行的硅通孔 (TSV) 構成。這些用于將裸片連接到中介層,并將中介層連接器連接到具有 BGA 焊盤圖案的封裝基板。

這些產品具有更高的 I/O 密度、更低的功耗和更低的傳輸延遲。這是通過微凸塊和 TSV 之間更小的走線長度和間距實現的。該技術的唯一顯著缺點是制造成本增加。

再看RDL封裝技術,再分布層 (RDL) 封裝技術不使用基板,而是將電介質和金屬直接沉積在晶圓的頂面上。該技術也稱為“扇出”技術。為了承載線路設計,構建了一個重新分布層,使得每個小Chiplet上的 I/O 端口圍繞設備成形。通過縮短電路的長度,RDL 提供更高的信號完整性(更低的損耗和失真)。至于EMIB ,則是一種使用嵌入有機材料中的薄硅晶片部分作為芯片到芯片互連基板的技術。高級產品成本較高的問題可以通過使用具有不同Chplet的橋接封裝來解決。這種混合封裝技術是基于基板和基于中介層的封裝的組合。通常小于 75 微米的薄硅層被涂在基板上并用于形成芯片間連接,這些層嵌入有機基板層中。該概念遵循 HDI PCB 中使用的 ELIC 中的相同想法,其中每層互連結構將多個芯片連接到絕緣(有機)基板中的內層。封裝的 EMIB 部分是一個硅橋,可在小芯片之間提供高帶寬連接。

先進封裝基板的助焊劑清洗劑:

半導體芯片封裝過程中通常會使用助焊劑和錫膏等作為焊接輔料,這些輔料在焊接過程或多或少都會有部分殘留物,還包括制程中沾污的指印、汗液、角質和塵埃等污染物。同時,半導體組裝了鋁、銅、鉑、鎳等敏感金屬和油墨字符、電磁碳膜和特殊標簽等相當脆弱的功能材料。這些敏感金屬和特殊功能材料對清洗劑的兼容性提出了很高的要求。

合明半水基清洗工藝解決方案,可在清洗芯片封裝基板的焊接殘留物和污垢的同時去除金屬界面高溫氧化膜,保障下一道工序的金屬界面結合強度;對芯片半導體基材、金屬材料擁有優良的材料兼容性,清洗后易于用水漂洗干凈。

歡迎使用合明科技半水基清洗劑W3300!

以上便是芯片封裝基板清洗,封裝基板的主要結構和生產技術的介紹,希望可以幫到您!

Tips:

【閱讀提示】

以上為本公司一些經驗的累積,因工藝問題內容廣泛,沒有面面俱到,只對常見問題作分析,隨著電子產業的不斷更新換代,新的工藝問題也不斷出現,本公司自成立以來不斷的追求產品的創新,做到與時俱進,熟悉各種生產復雜工藝,能為各種客戶提供全方位的工藝、設備、材料的清洗解決方案支持。

【免責聲明】

1. 以上文章內容僅供讀者參閱,具體操作應咨詢技術工程師等;

2. 內容為作者個人觀點, 并不代表本網站贊同其觀點和對其真實性負責,本網站只提供參考并不構成投資及應用建議。本網站上部分文章為轉載,并不用于商業目的,如有涉及侵權等,請及時告知我們,我們會盡快處理;

3. 除了“轉載”之文章,本網站所刊原創內容之著作權屬于合明科技網站所有,未經本站之同意或授權,任何人不得以任何形式重制、轉載、散布、引用、變更、播送或出版該內容之全部或局部,亦不得有其他任何違反本站著作權之行為。“轉載”的文章若要轉載,請先取得原文出處和作者的同意授權;

4. 本網站擁有對此聲明的最終解釋權。