POP芯片堆疊技術的趨勢和進步(PoP堆疊清洗劑)

POP芯片堆疊技術,是現代電子信息產品為提高邏輯運算功能和存儲空間而發展起來的一種新的高密度組裝形式。本文主要從設備技術的角度分析總結POP組裝工藝實現過程中的問題與對策。重點討論了POP組裝過程中主要工序工藝參數優化方法和范圍,探討了工藝過程控制中應關注的問題,這些都是確保POP芯片堆疊成功率的關鍵。

當前PoP的趨勢和進步

當前的趨勢是朝向更小化和更高密度的PoP發展,封裝到封裝的互連間距有0.5mm,這類封裝要求再回流時翹曲低至50μm,這類封裝也將會使底部PoP的底部上的焊球間距轉移到0.4mm,由于高

引腳數和受限的封裝面積(目標一般是12×12 mm或更小的封裝尺寸),需要在室溫下滿足共面規范,再回流時滿足在焊料熔點溫度以上的苛刻的翹曲規范。在表面組裝一側,為使微細球間距的PoP組裝和再回流同時發生,正在引入改進的表面組裝工藝。當今典型的表面組裝工藝包括在PCB上印刷焊膏、放置底部PoP、在熔劑內電鍍頂部PoP焊球、在底部PoP上放置頂部PoP、在清潔干燥的空氣中通過熔爐再回流將其熔化。引入的新型工藝包含了在焊劑或焊料糊中熔化頂部封裝焊球,可以提高再回流過程中頂部到底部的封裝互連的魯棒性。

PoP的未來

新型PoP及其變化正在冉冉升起,可以解決目前傳統PoP的一些弱點。例如,隨著封裝變得越來越薄,焊球間距越來越小,一種控制PoP翹曲挑戰的解決方式是在組裝到PCB上之前將頂部和底部封裝組裝到一起。雖然這削弱了PoP在靈活性上的優點,但是在基板組裝前進行“預疊層”是一項相對簡單的工藝,再回流過程中比較容易控制――再回流中PCB自身的翹曲。對預疊層PoP進行測試,可確保它是良好的,并且能夠展現出比單獨的頂部或底部PoP更低的翹曲,因此制造PoP類似于在PCB上組裝一個更加傳統的窄間距BGA。預疊層PoP非常吸引那些現在能為終端客戶提供低端邏輯器件和頂部存儲器件的器件制造商。這種選擇吸引的不是那些經營移動手持設備的終端客戶,而是期待為自己的產品采用PoP的客戶。

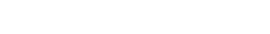

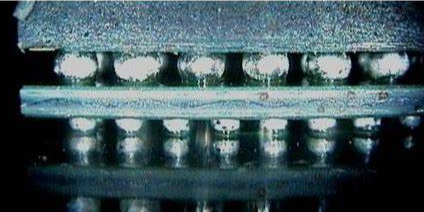

PoP堆疊芯片清洗:PoP堆疊芯片/Sip系統級封裝在mm級別間距進行焊接,助焊劑作用后留下的活性劑等吸濕性物質,較小的層間距如存有少量的吸濕性活性劑足以占據相對較大的芯片空間,影響芯片可靠性。要將有限的空間里將殘留物帶離清除,清洗劑需要具備較低的表面張力滲入層間芯片,達到將殘留帶離的目的。合明科技研發的清洗劑具有卓越的滲入能力,以確保芯片間殘留活性劑被徹底清除。

合明科技為您提供PoP堆疊芯片水基清洗全工藝解決方案。

針對先進封裝產品芯片焊后封裝前,基板載板焊盤、電子制程精密焊后清洗的不同要求,合明科技在水基清洗方面有比較豐富的經驗,對于有著低表面張力、低離子殘留、配合不同清洗工藝使用的情況,自主開發了較為完整的水基系列產品,精細化對應涵蓋從半導體封裝到PCBA組件終端,包括有水基清洗劑和半水基清洗劑,堿性水基清洗劑和中性水基清洗劑等。具體表現在,在同等的清洗力的情況下,合明科技的兼容性較佳,兼容的材料更為廣泛;在同等的兼容性下,合明科技的清洗劑清洗的錫膏種類更多(測試過的錫膏品種有ALPHA、SMIC、INDIUM、SUPER-FLEX、URA、TONGFANG、JISSYU、HANDA、OFT、WTO等品牌;測試過的焊料合金包括SAC305、SAC307、6337、925等不同成分),清洗速度更快,離子殘留低、干凈度更好。

想了解更多關于先進封裝產品芯片清洗的內容,請訪問我們的“先進封裝產品芯片清洗”產品與應用!

上一篇:Mini LED市場將迎來快速增長,電路板廠紛紛加入Mini LED這個高端局(MINI LED芯片清洗劑)

【閱讀提示】

以上為本公司一些經驗的累積,因工藝問題內容廣泛,沒有面面俱到,只對常見問題作分析,隨著電子產業的不斷更新換代,新的工藝問題也不斷出現,本公司自成立以來不斷的追求產品的創新,做到與時俱進,熟悉各種生產復雜工藝,能為各種客戶提供全方位的工藝、設備、材料的清洗解決方案支持。

【免責聲明】

1. 以上文章內容僅供讀者參閱,具體操作應咨詢技術工程師等;

2. 內容為作者個人觀點, 并不代表本網站贊同其觀點和對其真實性負責,本網站只提供參考并不構成投資及應用建議。本網站上部分文章為轉載,并不用于商業目的,如有涉及侵權等,請及時告知我們,我們會盡快處理;

3. 除了“轉載”之文章,本網站所刊原創內容之著作權屬于合明科技網站所有,未經本站之同意或授權,任何人不得以任何形式重制、轉載、散布、引用、變更、播送或出版該內容之全部或局部,亦不得有其他任何違反本站著作權之行為。“轉載”的文章若要轉載,請先取得原文出處和作者的同意授權;

4. 本網站擁有對此聲明的最終解釋權。